# 東海大學電機工程學系 碩士論文

# 高電壓垂直雙擴散場效電晶體元件(VDMOSFET)

V型溝槽終端結構設計

V-grooved Edge Termination Design for High Voltage VDMOSFET

研究生: 鄧傑文

指導教授: 龔正 博士

中華民國 104年6月30日

# 東海大學電機工程學系碩士學位考試委員審定書

電機工程學系研究所 鄧傑文 君所提之論文

高電壓垂直雙擴散場效電晶體元件(VDMOSFET) V型溝槽終端結構設計

經本考試委員會審查,符合碩士資格標準。

學位考試委員會召集人: 黃智 (簽章)

委員: 街

8 .

中華民國 104 年 06 月 30 日

# 致謝

完成此篇論文以及碩士學位,首先要感謝指導教授龔正老師,從 大學到碩士期間的指導,開啟對半導體領域的興趣。在許多觀念不足 的情况下,老師耐心教導,並在其他課餘時間以及假日開課指導,使 我對半導體基本的觀念大大的提升。也很感謝從我學習生涯中幫助過 我的指導老師們,對於我的處事態度以及學習態度都因為有了妳們的 認同讓我覺得有妳們真好。也很感謝實驗室的學長紀雅軒、林政佑、 林德裕,以及同學家慧、俊富、湧昌、新郇、柏豪、勝發以及鄭慎學 妹甚至是 WEN LAB 的學長同學們,陪我經歷這些刻苦歡樂的日子 在無時無刻提供協助、教導、掩護,因為有了妳們使得我在實驗室裡 的生活有了不一樣的歡樂。特別要感謝雅軒學長、家慧同學,本來從 不懂半導體的我,願意在實驗室裡幫助我教導我雖然讓妳們兩位時常 為我生氣、暴怒過,還讓你們時常擔心我,因為我知道這都是妳們的 用心以及愛的關懷。最後要感謝從小栽培我到大的父母,在我人生中 遇到的風風雨雨、困難挑戰都願意默默的支持我,讓我完成碩士學位。

# 摘要

功率 VDMOSFET 由於其優異特性而被廣泛地應用於開關電源、 汽車電子等領域,是功率元件的主流產品之一。功率 VDMOS 元件由 於終端 pn 接面的曲率效應,其高壓阻斷能力受到限制,為了提高高 壓阻斷能力,接面終端技術被廣泛採用,是現代功率元件的關鍵技術 之一。本文首先介紹各種 VDMOSFET 接面終端技術及其最新研究和 發展,然後介紹自行研製的元件。模擬結果顯示在耐壓達到 750V 的 條件下,使用了新想法在 VDMOSFET 表面層採用 V 型溝槽的終端 結構可以減小元件的面積而不會降低崩潰電壓值,同時可以使高電場 遠離元件核心區域,增強元件的可靠度,證明 V 型槽終端結構設計是 成功的。

# **Abstract**

VDMOSFET due to its excellent properties and it is widely used in switching power supplies, automotive electronics and other fields, is one of the mainstream products of power components. VDMOS element's pn junction due to terminal curvature effect, the high voltage blocking capability is limited. In order to improve high voltage blocking capability one of the key technologies, junction terminal technology, is widely used in modern power components. This paper describes various VDMOSFET junction terminal technologies and their latest research and development, and to introduce the developed components of my own. Simulation results show that under the conditions of a breakdown voltage of 750V, using the V-groove terminal structure can reduce VDMOSFET's area without reducing the breakdown voltage, while allowing the high electric field area move away from the core element, which can enhanced the device reliability.

# 目錄

| 口試委員會審定書        | I   |

|-----------------|-----|

| 致謝              | II  |

| 摘要              | III |

| Abstract        | IV  |

| 目錄              | V   |

|                 | VII |

| 1.7/2           | XII |

| 政謝              |     |

| tract           |     |

| 1.2.研究方法        | 1   |

| 1.3.論文架構        | 1   |

| 第二章 功率元件及終端結構理論 | 3   |

| 2.1.功率元件基本參數    | 3   |

| 2.1.1 崩潰電壓      | 3   |

| 2.1.2 導通電阻      | 3   |

| 2.1.3 效能指標      | 4   |

| 2.2.崩潰機制        | 4   |

| 2.2.1 基納崩潰      | 5   |

| 2.2.2 穿透崩潰                                      | 5  |

|-------------------------------------------------|----|

| 2.2.3 轉折崩潰                                      | 6  |

| 2.2.4 雪崩崩潰                                      | 7  |

| 2.2.5 氧化層崩潰                                     | 9  |

| 2.3.終端結構理論                                      | 9  |

| 2.3.1 終端結構簡介                                    | 9  |

| 2.3.2 金屬場板結構                                    | 16 |

| 2.3.3 浮動環結構                                     | 16 |

| 2.3.4 接面延伸結構                                    | 17 |

|                                                 | 17 |

| 2.3.6 終端結構總結                                    | 18 |

| 2.4. VDMOSFET (Vertical Double diffused MOSFET) | 20 |

| 第三章 平面結構終端結構製程設計與電性模擬                           | 23 |

| 3.1 平面終端結構                                      | 23 |

| 3.1.1 平面終端元件製作流程                                | 23 |

| 3.1.2 元件結構                                      | 23 |

| 3.1.3 製程規劃                                      | 24 |

| 3.1.4 電性模擬                                      | 33 |

| 第四章 V 刑                                         | 41 |

| 4.1 | V型溝槽終端結構              | .41 |

|-----|-----------------------|-----|

| 4   | .1.1 設計原理             | .41 |

| 4   | .1.2 改進功率元件模擬         | .43 |

| 4   | .1.3 120um 終端結構之改善與模擬 | .59 |

| 第丑  | <b>五章 結論</b>          | .72 |

| 第プ  | <b>、章 參考文獻</b>        | .74 |

# 圖目錄:

| 圖 | 2-1:基納崩潰示意圖                                   | 5  |

|---|-----------------------------------------------|----|

| 圖 | 2-2:穿透崩潰示意圖                                   | 6  |

| 圖 | 2-3:轉折崩潰之I-V特性圖                               | 7  |

| 圖 | 2-4:雪崩崩潰示意圖                                   | 9  |

| 圖 | 2-5: PN 接面示意圖                                 | 13 |

| 圖 | 2-6:場板(Field Plate)結構示意圖                      | 14 |

| 圖 | 2-7:浮動環(Floating Ring)結構示意圖                   | 14 |

| 圖 | 2-8:接面延伸(Junction Termination Extension)結構示意圖 | 15 |

| 圖 | 2-9:降低表面電場(RESURF)結構示意圖                       | 15 |

| 圖 | 2-10:(a)垂直式通道金氧半場效電晶體(VMOSFET)結構示意圖           | 16 |

| 圖 | 2-10:(b)雙擴散式金氧半場效電晶體(DMOSFET)結構示意圖            | 17 |

| 圖 | 2-10:(c)溝槽式金氧半場效電晶體(UMOSFET)結構示意圖             | 17 |

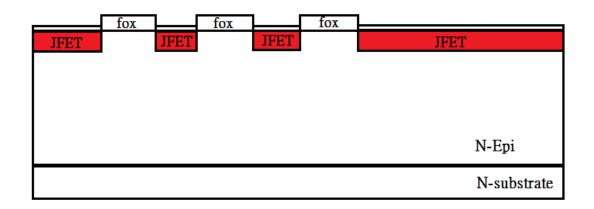

| 圖 | 3-1:傳統平面終端結構圖                                 | 24 |

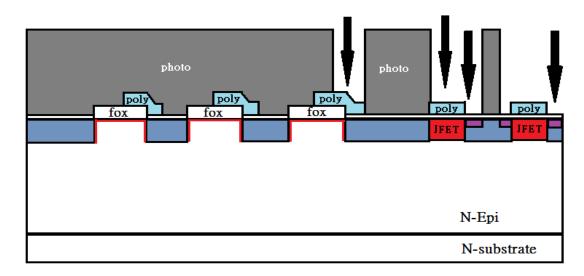

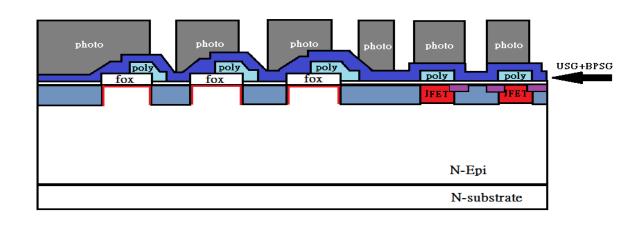

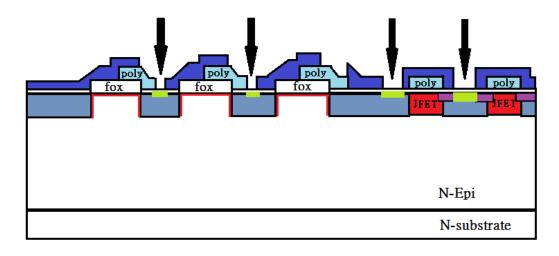

| 圖 | 3-2:製程步驟一                                     | 24 |

| 圖 | 3-3:製程步驟二                                     | 25 |

| 圖 | 3-4:製程步驟三                                     | 25 |

| 圖 | 3-5:製程步驟四                                     | 26 |

| 圖 | 3-6: 製程步驟五                                    | 26 |

| 邑 | 3-7:製程步驟六                                                      | 27 |

|---|----------------------------------------------------------------|----|

| 昌 | 3-8:製程步驟七                                                      | 27 |

| 昌 | 3-9:製程步驟八                                                      | 28 |

| 圖 | 3-10:製程步驟九                                                     | 28 |

| 昌 | 3-11:製程步驟十                                                     | 29 |

| 圖 | 3-12:製程步驟十一                                                    | 29 |

| 圖 | 3-13:製程步驟十二                                                    | 30 |

| 圖 | 3-14:製程步驟十三                                                    | 30 |

| 昌 | 3-15:製程步驟十四                                                    | 31 |

| 圖 | 3-16:製程步驟十五                                                    | 31 |

| 圖 | 3-17:製程步驟十六                                                    | 32 |

| 圖 | 3-18:製程步驟十七                                                    | 32 |

| 圖 | 3-19:平面終端結構模擬圖                                                 | 33 |

| 昌 | 3-20:元件結構參數對應圖                                                 | 33 |

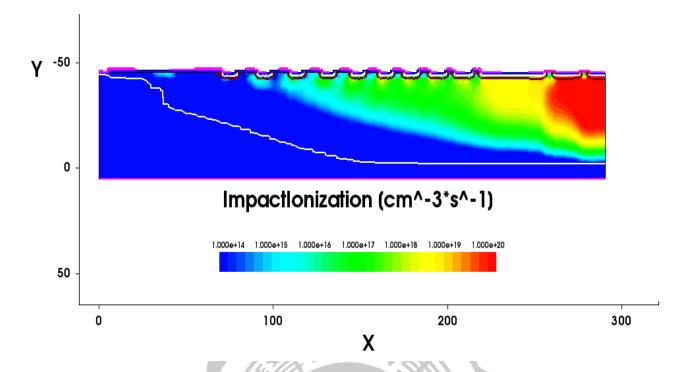

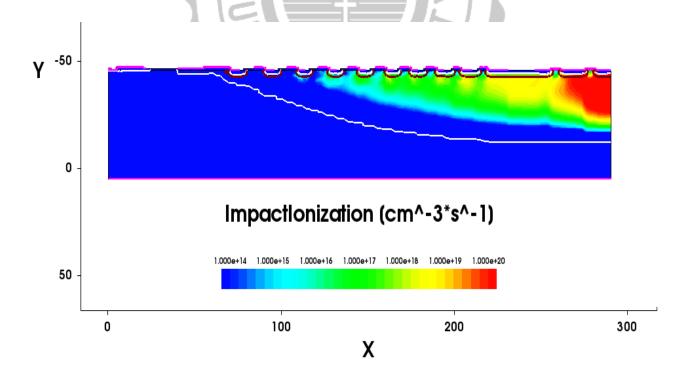

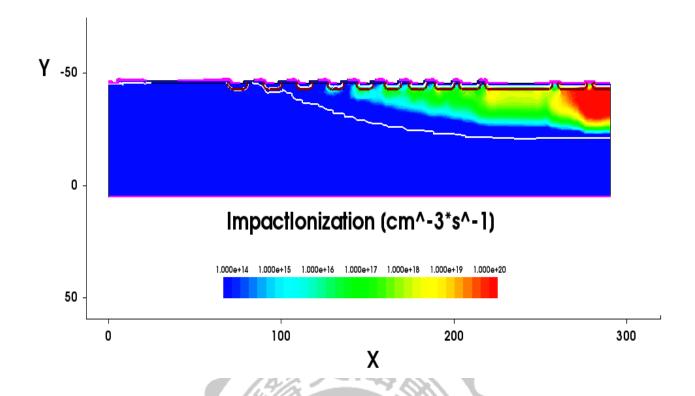

| 置 | 3-21(a):N-Epi 濃度為1×10 <sup>14</sup> cm <sup>-3</sup> 之 IIGR 分佈 | 34 |

| 圖 | 3-21(b):N-Epi 濃度為3×10 <sup>14</sup> cm <sup>-3</sup> 之 IIGR 分佈 | 35 |

| 昌 | 3-21(c):N-Epi 濃度為5×10 <sup>14</sup> cm <sup>-3</sup> 之 IIGR 分佈 | 35 |

| 圖 | 3-21(d):N-Epi 濃度為7×10 <sup>14</sup> cm <sup>-3</sup> 之 IIGR 分佈 | 36 |

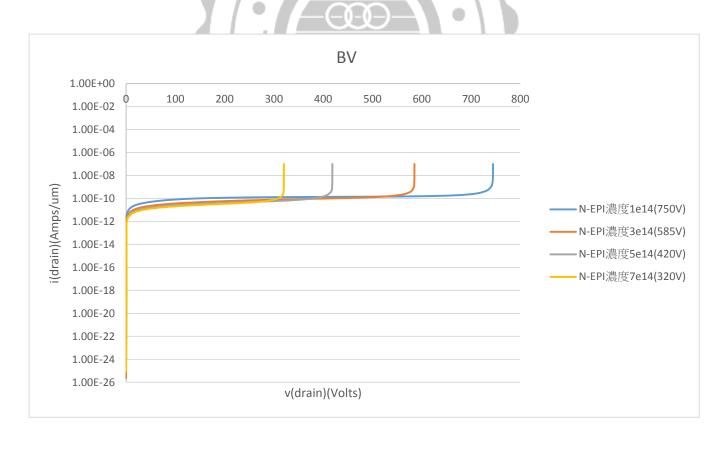

| 圖 | 3-22:VDMOSFET 平面終端結構崩潰雷壓                                       | 36 |

| 圖 | 3-23:表面電場切割圖               | 37  |

|---|----------------------------|-----|

| 圖 | 3-24:電場分佈圖                 | .38 |

| 圖 | 4-1:KOH 蝕刻比例圖              | .42 |

| 圖 | 4-2:V 型溝槽終端結構模擬圖           | .42 |

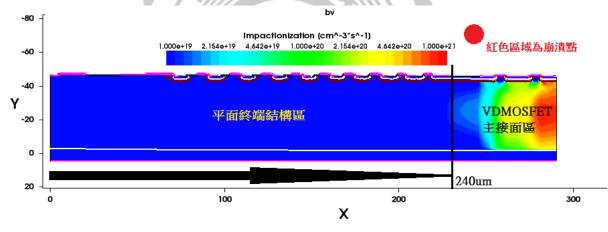

| 圖 | 4-3:平面 V 型溝槽終端結構崩潰電場圖      | .43 |

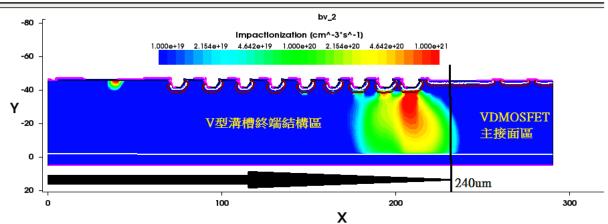

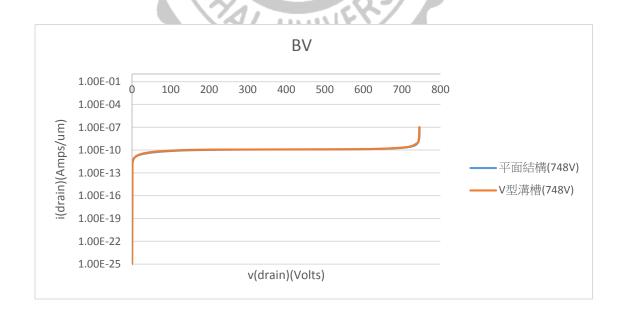

| 圖 | 4-4:平面與 V 型溝槽終端結構崩潰電壓曲線圖   | .44 |

| 圖 | 4-5:8個與7個V型溝槽終端結構          | .45 |

| 圖 | 4-6:6個與5個V型溝槽終端結構          | .45 |

| 圖 | 4-7:4個V型溝槽終端結構             | .46 |

| 圖 | 4-8:各溝槽的崩潰電壓曲線圖            | .46 |

|   |                            | .47 |

| 圖 | 4-10:5個V型溝槽電場切割圖           | .48 |

| 圖 | 4-11:終端結構240 um 長的電場分布圖    | .49 |

| 圖 | 4-12:終端結構 240 um 元件的崩潰電壓曲線 | .50 |

| 圖 | 4-13:240um 切割位置圖           | .50 |

| 圖 | 4-14:終端結構 190 um 長的電場分布圖   | .51 |

| 圖 | 4-15:終端結構 190 um 長的崩潰電壓    | .51 |

| 圖 | 4-16:190um 切割位置圖           | .52 |

| 晑 | 4-17:終端結構 170 um 長的雷場分布圖   | .53 |

| 圖 | 4-18:終端結構 170 um 長的崩潰電壓     | .53 |

|---|-----------------------------|-----|

| 圖 | 4-19:多場限環結構邊界峰值電場和空乏區外邊界示意圖 | .56 |

| 圖 | 4-20:120um平面終端結構            | .59 |

| 圖 | 4-21: 120um 崩潰電壓曲線圖         | .60 |

| 圖 | 4-22:120um終端結構崩潰區及電位圖       | .61 |

| 圖 | 4-23:5 環拉進環間距及電位圖 1(120um)  | .61 |

| 圖 | 4-24:5 環拉進環間距及電位圖 2(120um)  | .62 |

| 圖 | 4-25:5 環拉進環間距及電位圖 3(120um)  | .62 |

| 圖 | 4-26:5 環拉進環間距及電位圖 4(120um)  | .63 |

| 圖 | 4-27:5 環拉進環間距及電位圖 5(120um)  | .63 |

|   | 4-28:各5環拉進環間距之崩潰電壓曲線        |     |

| 圖 | 4-29:120um 平面終端結構圖          | .65 |

| 圖 | 4-30:120um平面終端結構圖及電位圖       | .65 |

| 昌 | 4-31:120um平面終端結構圖及電位圖       | .68 |

| 昌 | 4-32:120um 5 個 V 型溝槽終端結構    | .69 |

| 昌 | 4-33:120um 4 個 V 型溝槽終端結構    | .69 |

| 圖 | 4-34:120um 3 個 V 型溝槽終端結構    | .70 |

| 圖 | 4-35:120um 2 個 V 型溝槽終端結構    | .70 |

| 圖 | 4-36:120um 1 個 V 型溝槽終端結構    | .71 |

# 表目錄:

| 表 | 2-1:五種終端結構比較               | 19 |

|---|----------------------------|----|

| 表 | . 3-1:VDMOSFET 平行終端結構濃度參數表 | 34 |

| 表 | 4-1:KOH 蝕刻優缺點              | 41 |

| 表 | . 4-2:環寬與環間距之前後長度表         | 64 |

| 表 | 4-3:接面雷壓比較表                | 67 |

# 第一章 緒論

#### 1.1 研究動機

功率元件應用在電力電子極為廣泛,如切換開關、馬達控制、消費性電子與不斷電系統等等。而且功率元件要求低耗電、高耐壓、切換速度快、安全操作區大、元件尺寸不斷要求節省成本越做越小。在尺寸越小操作規格無法相對降低的情況下元件內部電場明顯增加許多,面臨到的問題也接踵而至,使得我們要使用新的結構來改善這些問題。

#### 1.2 研究方法

本文首先介紹各種 VDMOSFET 接面終端技術 <sup>[1-6]</sup>及其最新研究和發展,然後介紹自行研製的元件。模擬結果顯示在耐壓達到 700V以上的條件下且終端結構小於120um<sup>[7-14]</sup>,使用了新想法在 VDMOSFET 表面層採用 V 型溝槽的終端結構可以減小元件的面積而不會降低崩潰電壓值。同時可以使高電場遠離元件核心區域,增強元件的可靠度,證明 V 型槽終端結構設計是成功的。

#### 1.3 論文架構

此次研究目標為平面型終端結構與 V 型溝槽終端結構的元件來做比較,使功率元件操作在高壓下,比較兩者的耐壓高低,電場分佈以及電力線的密度,期許獲得較佳的元件性能。從論文的第二章開始,

我們將先了解崩潰機制、改善崩潰機制的方法以及終端結構的原理。 第三章將探討 VDMOS 的平面終端結構,摻雜面積之結構大小,環的 數量、環的間距以及環的寬度等。第四章則是探討 VDMOSFET 從平 面改良成 V 型溝槽終端結構的構造以及優點,兩者模擬都是利用 Sentaurus 軟體進行設計及電性模擬。從模擬結果分析這兩種型態的 終端結構,並且利用外界推導的公式進行結構設計。此外,透過平面 與 V 型溝槽的終端結構比較兩者差異,依據模擬結果,我們從電力線 分布的密度、電場分佈、表面電場大小和崩潰電壓逐步探討比較平面 與 V 型溝槽的終端結構。第五章是整體的結論。

# 第二章:功率元件及終端結構理論

# 2.1 功率元件基本參數

## 2.1.1 簡介

回顧功率金氧半場效電晶體的相關發展之前,必須先了解基本的功率金氧半場效電晶體的操作機制,以及重要的元件特性參數。本節利用 N 型垂直式通道雙擴散金氧半場效電晶體(N-channel Vertical DMOSFET),簡稱 VDMOSFET)作為例子,分別針對元件的導通,耐壓及崩潰機制進行介紹。

# 2.1.2 崩潰電壓(Breakdown Voltage)

在積體電路中,功率元件被當作開關來使用,施加外加電壓,使元件工作在逆偏情形,元件僅產生微小的漏電流。當逐漸增加外加電壓,終於會使得元件流通大量電流,此時外加電壓的值,稱為崩潰電壓。崩潰情況有:基納崩潰(Zener Breakdown)、穿透崩潰(Punch-Through Breakdown)、轉折崩潰(Snapback Breakdown)、以及雪崩崩潰(Avalanche Breakdown)等,以上崩潰情形會在崩潰機制中詳述。本元件在模擬中定義元件電流大於1×10<sup>-7</sup>(Amps/um),此元件崩潰。

# 2.1.3 導通電阻(On-resistance)

當功率元件操作在順偏工作情形,外加偏壓與導通電流 I-V 曲線的斜率乘上元件的面積其值即為導通電阻,本研究以公式(2.1)計算導

通電阻。

$$R_{ON,sp} = \frac{\Delta V}{\Delta I} \times A \tag{2.1}$$

# 2.1.4 效能指標(Efficiency Index)[15]

功率元件是用來處理電能的問題。因為功率為電流和電壓的乘積, 所以功率元件要能夠處理大電流以及耐高壓,也必須減少操作時的能 耗。所以功率元件在設計的過程中,須考慮到兩個目標,首先考慮崩 潰電壓,接著再考慮導通電阻,但是這兩個目標在設計過程中是互相 影響的。一般希望功率元件能達到使用額定電壓、低導通電阻的特性。 因此利用公式(2.2)效能指標(Efficiency index)值來判斷該元件性能的 優劣,此值越高表示該功率元件導通性能越好。

$$Effciency = \frac{Breakdown\ Voltage}{On - Resistance} (\frac{V}{m\Omega - cm^2})$$

# 2.2 崩潰機制[16]

在功率元件設計過程中,元件的耐壓能力,是需要優先考慮的。 功率元件承受高電壓主要是依靠元件內 PN 接面的空乏區。對於功率 元件施加反向偏壓,元件內部的 PN 接面產生空乏區。當逆向偏壓高 出元件的崩潰電壓,元件內部的 PN 接面崩潰,元件的電流迅速增加, 此情況稱為崩潰,接著介紹各種崩潰情形。

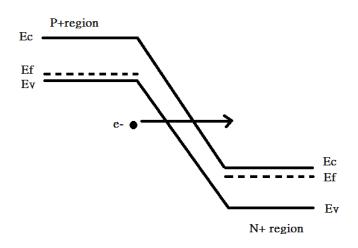

#### 2.2.1 基納崩潰

基納崩潰是由穿隧效應所產生的崩潰情形,對 PN 接面施加逆向偏壓,若 P 型與 N 型載子皆為重摻雜時,接面產生一個大電場約  $1 \times 10^6 (V/cm)$ ,因空乏區的厚度比輕摻雜還短,使得 P 型半導體價帶內的電子會穿隧到 N 型半導體的傳導帶,如圖 2-1 所示,導致元件發生崩潰。因基納崩潰的電壓值都在六伏特以下,所以基納崩潰多應用在穩壓電路上,功率元件必須避免此種崩潰發生。

圖 2-1:基納崩潰示意圖

# 2.2.2 穿透崩潰

穿透崩潰屬於雙接面崩潰,以 MOS 電晶體為例,外加偏壓為逆向偏壓,汲極空乏區的大小隨著逆向偏壓而增加。逐漸加大逆向偏壓, 使得汲極的空乏區與源極的空乏區相接,形成連續接面,如圖 2-2 所 示。源極的多數載子便直接流入汲極,產生大電流,導致元件崩潰。 只要增加元件尺寸,讓空乏區有足夠的延伸距離便能夠解決穿透崩潰 發生。

圖 2-2:穿透崩潰示意圖

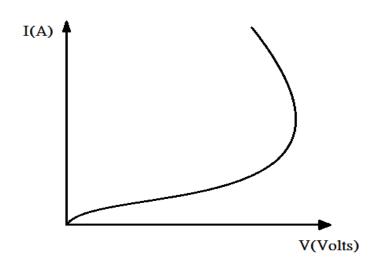

# 2.2.3 轉折崩潰

轉折崩潰是由於元件內部有過多的電流使得寄生於元件內的電晶體導通所產生的崩潰,如圖 2-3。

圖 2-3:轉折崩潰之 I-V 特性圖

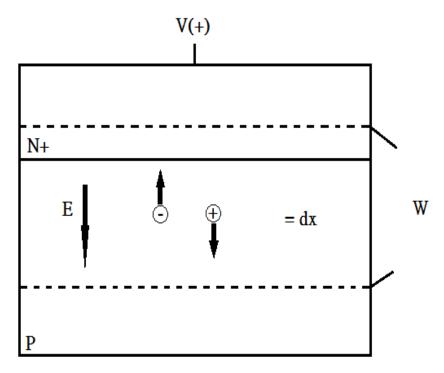

# 2.2.4 雪崩崩潰

PN 接面,兩邊皆非重摻雜的情況下,施加逆向偏壓值,接面電場隨著逆向偏壓增加。當載子獲得足夠的能量開始撞擊晶格原子,產生電子-電洞對(Electron-hole pair EHP)。碰撞過產生的電子-電洞對隨即亦被電場加速,獲得足夠的能量撞擊晶格原子,而產生新的電子-電洞對,若此現象一再重複,這些新產生的電子-電洞對受到電場作用,使得元件電流增加,稱之為雪崩崩潰。此情形都是操作於高電壓下,故功率元件崩潰機制以雪崩崩潰為主。接著介紹如何使用游離積分定義崩潰,如圖 2-4 所示,在游離化的過程中,產生電子-電洞對的程度,定義為游離係數。 $\alpha_n$ 為電子在空乏區行進一公分所產生電子-電洞對的數量、 $\alpha_p$ 為電洞在空乏區行進一公分所產生電子-電洞對的數量。

受到接面電場影響,電子往  $N^+$ 區域移動,電洞往 P區域移動,假設經過的距離為 dx,電子與電洞撞擊晶格產生 M(x)組電子-電洞對。

$$M(x) = 1 + \int_0^x \alpha_n M(x) dx + \int_x^w a_p M(x) dx$$

(2.3)

W為空乏區的寬度,解以上數式,可得

$$M(x) = M(0) \exp\left[\int_0^w (\alpha_n - \alpha_p) dx\right]$$

(2.4)

代入原式,得 x=0 的解為

$$M(0) = \{1 - \int_0^w a_p \exp\left[\int_0^x \alpha_n - \alpha_p \, dx\right] dx\}^{-1}$$

(2.5)

故

$$M(x) = \frac{\exp[\int_0^x (\alpha_n - \alpha_p)]}{1 - \int_0^w \alpha_p \exp[\int_0^w (\alpha_{n-}\alpha_p) dx] dx}$$

(2.6)

當M值趨近無限大,即定義為崩潰之條件,亦即分母趨近於零,

得下式稱游離化積分

$$\int_{0}^{w} \alpha_{p} \exp\left[\int_{0}^{w} (\alpha_{n} - \alpha_{p}) dx\right] dx = 1$$

(2.7)

為了簡化運算,令

$$\alpha_{\rm n} = \alpha_{\rm p} = \alpha \tag{2.8}$$

得常用的簡式如下

$$\int_0^w \alpha \cdot dx = 1 \tag{2.9}$$

其中 $\alpha = 1.8 \times 10^{-3} \cdot E^7$ ,利用游離化積分判斷元件何時崩潰,游

離化積分值近於 1 ,也就是增值係數 M(x)近於無限大的時候,元件便發生崩潰。

圖 2-4:雪崩崩潰示意圖

# 2.2.5 氧化層崩潰

氧化層崩潰是由於橫跨氧化層的電場值達到臨界電場,所引發的 崩潰情形,材料內部發生場效發射現象產生大電流,導致元件崩潰。 氧化層夠厚的元件便不會發生此崩潰情形。

## 2.3 終端結構理論

## 2.3.1 終端結構簡介

功率積體電路及元件在相關電機電子產品領域中應用日漸增多,

但功率元件的設計製造及工作條件則有別於一般的傳統元件,例如可 承受的電壓及電流範圍、功率、元件的耐用性、可靠度和安全操作範 圍等,其設定的標準和一般 IC 有很大的不同,特別是功率元件在電 壓的操控方面,25 伏至 6000 伏以上的應用皆有。功率元件的進步為 電力電子帶來革命性的發展,而且現今的市場針對不同的應用提供了 很多可用的元件。如 Power MOSFET 是低功率元件的主流, 開關的 切換速度快是其最大的優點,在高頻操作的電路上極具吸引力,主要 應用在RF電路、切換式的電源供應器及馬達控制電路等。中功率元 件首推 IGBT(Insulated Gate Bipolar Transistor),在 600~2500 伏電壓及 10K 瓦功率的等級上,已取代了功率雙載子接面電晶體(power BJT)、 達靈頓電晶體(Darlington transistor)、MOSFET和GTO thyristor,主要 應用有交流馬達驅動、感應式加熱系統、不斷電電源供應器及切換式 電源供應器等。如閘流體(Thyristor)也稱為 SCR(Silicon-controlled rectifiers),擁有最高功率密度的元件,可負載 3500 安培的順向電流 且順向壓降小於2伏,並可以支撐大於6000伏的反向偏壓,閘流體 是一個單獨的元件,被歸類在百萬瓦特的功率等級,如 12k 伏/1.5 安 培、7.5k 伏/1.65k 安培及 6.5k 伏/2.65k 安培等,經常被應用在高壓直 流轉換器、自耦變壓器、大功率的電源供應器及直流馬達驅動等。

功率元件操控電壓的能力取決於當元件內部電場變得很大時,雪

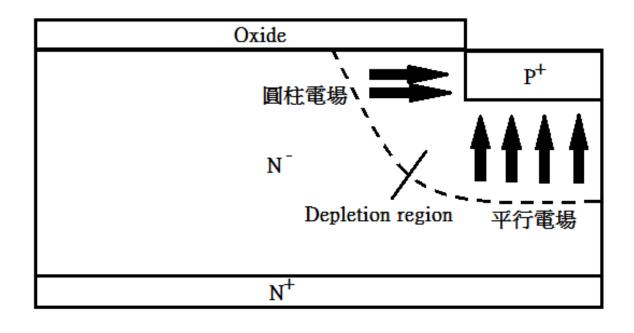

崩崩潰的發生。高電場會發生在元件內部電流流過的地方或是元件邊界,因此設計上須小心注意電場在內部或是邊界的部分,以確保元件能承受高壓,且盡可能的使元件的崩潰電壓能和元件材料本身特性一樣,以達到最佳化。平行擴散技術常常被使用在功率元件中,藉由氣體擴散或離子佈植來形成接面,然而,雜質會橫向擴散,程度約為垂直擴散的百分之八十五,當接面由方形的窗口形成,圓柱和圓球形接面會在四周半隨而生,如圖 2-5。箭頭代表電場線,接面內部的電場較均勻,其崩潰電壓和平行接面的崩潰電壓相同,但在邊緣的地方,電場線的聚集變的更緊密,使得此處的崩潰電壓將小於平行接面的崩潰電壓。由柏桑方程式(Poisson equation)可推導出式子(2.10)(2.11)

$$\frac{1}{r}\frac{d}{dr}\left[r\frac{dV}{dr}\right] = \frac{1}{r}\frac{d}{dr}(rE) = \frac{qN_A}{\varepsilon\varepsilon_0}$$

(2.10)

$$E_{m,PP} = \frac{qN_A}{\varepsilon\varepsilon_0}r_d \tag{2.11}$$

r<sub>i</sub>: 柱狀接面的深度 r<sub>d</sub>: 輕摻雜端的空乏區半徑

NA: 輕摻雜端的載子濃度

E<sub>m,PP</sub>: 平行接面的最大電場

$E_{m,CYL}(r_i)$ : 圓柱接面的最大電場

由(2.10)(2.11)可得(2.12)

$$\frac{E_{m,CYL}}{E_{m,PP}} = \frac{r_d}{2r_j} \tag{2.12}$$

如果接面深度是 1μm,空乏區寬度是 50μm,圓柱接面的最大電場將是平行接面最大電場的 25 倍,也就證明圓柱接面的電場線會較密集,而使得接面提早崩潰。

實際的元件中,因為長度不可能無限大,平行接面一定會被終止在邊界上。而在邊界上的接面將彎曲,圓柱和球形的接面因此產生,這種情形是無可避免的。唯一可以做的事,是將終端區域的電場設計成接近平行接面,使電位重新分佈,進而使在矽基板內的電場能分佈到任何可到達的區域,即是終端結構設計的唯一目的。顯而易見地,電位差降在愈大的區域,會有愈小的電場和崩潰電流。一般來說,功率元件終端結構的崩潰電壓會小於其內部。即使元件本身可以承受較高的電壓,終端結構發生崩潰後,整個元件操作的電流仍會持續變大,使操作的功率超過安全值導致元件毀壞。因此已經有許多接面的終端結構被發展出來,大部分訴求的重點是在製程的簡化、效率(efficiency)、相同電壓下消耗的面積上。這裡的效率是指能達到平行板結構崩潰電壓的百分比。

每一種結構都有其最重要的設計參數,如何控制好這些參數使其達到崩潰電壓的最佳化,將會影響製程設計的簡單與否。在此簡單介紹幾種現今微電子領域中常見的終端結構:場板(Field Plate)結構、浮動環(Field Ring)、接面邊界延伸(Junction Termination Extension)以及降低表面電場(RESURF)結構,圖 2-6 到 2-9 為這四種終端結構的基本結構圖<sup>[17]</sup>。除了降低表面電場結構只能用在水平式結構,另外三種結構的電極都能做成水平式或垂直式的,易與積體電路整合在一起,如 Lateral power diode<sup>[18-19]</sup>、LDMOSFET<sup>[20]</sup>等水平式的功率元件及Trench Gate、Power MOSFET、IGBT<sup>[21]</sup>等垂直式的功率元件。

圖 2-5: PN 接面示意圖

圖 2-6:場板(Field Plate)結構示意圖

圖 2-7:浮動環(Floating Ring)結構示意圖

圖 2-8:接面延伸(Junction Termination Extension)結構示意圖

圖 2-9:降低表面電場(RESURF)結構示意圖

## 2.3.2 金屬場板結構

金屬場板結構如圖 2-6,低電壓的電極向外延伸,延伸出來的電極相對於基底為負電壓,就像在P+/N接面旁邊多並聯了一個電容,能多吸引一些正電荷,也就等於將基底多空乏了一些,因此空乏區由P/N接面的地方向外延伸,接面尖角處較密集的電場獲得了緩衝,崩潰電壓藉此能再提升。此結構最重要的設計參數是氧化層的厚度和電極延伸的長度。電極的延伸長度有一個最佳的條件,而如果氧化層太厚,延伸電極在基底感應的電荷太少,等於沒發揮效用,如果太薄,在延伸電極的邊緣會產生更大的電場,可能比主要P+/N接面的電場還大,元件反而提早崩潰。

## 2.3.3 浮動環結構

浮動環結構如圖 2-7,在主要P+/N接面的附近,藉由多植入P+的well 和 EPI 形成額外的空乏區與原有的空乏區產生交互作用,增加RESURF 效果,使整個漂移區更快完全空乏,大幅提高電晶體的耐壓能力,此技術也因此被稱為 Double RESURF 技術。在技術上,P形浮動環的離子植入劑量、離子植入深度、光罩圖案位置都必須掌控的非常精確才能夠顯現它的效果,因此有製程不易的缺點。但是由於製程技術日漸進步,目前此結構已經廣泛地運用在各種元件之中。

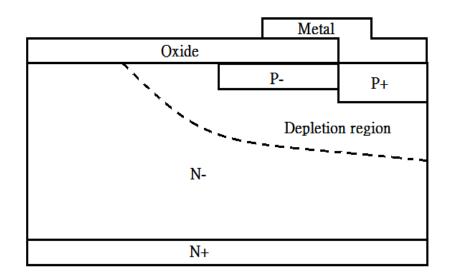

#### 2.3.4 接面延伸結構

接面邊界延伸如圖 2-8,在緊鄰主要的P+/N接面旁邊多植入較淺的P-,因為是和P+低電壓端連接著,P+/N接面會逆偏,空乏區由此延伸的接面能再多往外擴張,而此結構最重要的設計參數就是延伸出的P濃度,有一最佳的濃度使達到最大的崩潰電壓,如果濃度太淡,很快被完全空乏掉,崩潰點又會回到主接面,使得P層無法發揮效用。如果P太濃,P層很難被空乏,使P層邊緣的空乏區很小,崩潰電壓反而被此限制。另外,P層的延伸寬度也須控制好,取得最佳化條件。

## 2.3.5 RESURF 結構

降低表面電場結構如圖 2-9,在設計高電壓和低導通電阻的水平式結構上,RESURF 是最有效的方法之一,它已成功被應用在許多高電壓結構上,如二極體、LDMOSFET、LIGBT 及JFET<sup>[22-25]</sup>等,此結構最大可承受的逆偏電壓範圍,可已從幾十伏特到幾千伏特。其基本結構包含一個高電阻值的 P型基底,上面有一N<sup>-</sup>磊晶層,此N<sup>-</sup>層的横向被一P<sup>+</sup>包住,而兩個二個主要接面因此型成,一個是P<sup>+</sup>/N<sup>-</sup>接面,另一個是P<sup>-</sup>/N<sup>-</sup>接面,加大電壓下,磊晶層在特定的厚度下,會完全空乏,且使P<sup>+</sup>/N<sup>-</sup>的接面電場小於臨界電場即表面電場不使元件崩潰,而P<sup>-</sup>/N<sup>-</sup>接面的電場近似臨界電場,因此可以達到比較理想的基底崩潰雷壓。

## 2.3.6 終端結構總結

場板結構方面,製程上最為簡單,只要一個延伸的金屬板,且可以在金屬化製程步驟一起完成,但是在場板邊緣下方的矽基板位置,由於電位劇烈變化,將造成一個比主要接面區更大的電場,此電場如果超過矽的介電強度,即發生崩潰。因此,這個電場限制了崩潰電壓,使單一場板的結構,大多應用在低電壓的範圍。

以浮動環來說,有高效率及製程簡單是此結構的優點,因為周圍的井區可以伴隨著主要元件區一起製作,不須多一道製程步驟或光罩,但井間的距離大大地影響崩潰電壓。如何找出最佳化是此結構設計上非常困難的地方,而且如果要做到耐較高的崩潰電壓,愈靠近外圈的井,彼此間的距離必須愈來愈大。因此最後將消耗許多面積,較不符合降低製程成本的需求。

接面邊界延伸方面,類似浮動環,但多了一離子佈植的步驟去形成邊界延伸的區域。目的是要正好能被完全空乏,提高空乏區寬度,進而提高崩潰電壓。但設計上,如果要能承受較高的電壓,就需要多幾次離子佈植將邊界延伸出去,每一次佈植的濃度和寬度,要達到最佳化設計,將變得非常困難,而寬度也會消耗更多的面積。另外,此結構的效率會嚴重受到氧化層和矽基板介面電荷的影響。因為延伸區域的介面電荷會影響此處電位分佈,進而影響到空乏區的分佈,使崩

潰電壓不在最佳化處。

降低表面電場結構方面,優點為導通狀態下的高電流傳導區域和 截止狀態下的高逆偏電壓區域是分開的。因此能較容易同時達到高崩 潰電壓及低導通電阻,且設計和製程簡單及消耗面積較少。缺點為崩 潰電壓極易受到磊晶層特性的影響和無法與垂直結構的元件整合。表 2-1 為五種終端結構的比較。

|       | Field plate   | Floating field | JTE   | RESURF       | SIPOS |

|-------|---------------|----------------|-------|--------------|-------|

|       | 氧化層厚度、        | Ring 劑量、       | 接面延伸長 | 磊晶層濃度        | 無     |

| 關鍵參數  | 場板長度          | 表面電荷           | 度、表面電 | 及厚度          |       |

|       |               |                | 荷     |              |       |

| 設計難易度 |               | 3              | . 6   |              | •     |

| 製程難易度 | ••            |                | VIV   |              | ••••  |

| 效率    | •             | ) <u> </u>     | 55    | ••••         | •••   |

| 消耗面積  | ••••          | •••            | •••   | •••          | ••    |

| 其他    | 只能配合低崩<br>潰電壓 | 設計難度較高         |       | 只能配合水<br>平結構 | 漏電流較大 |

表 2-1 五種終端結構比較

備註:●的數量越多代表難度越高、效率越好、消耗面積越多 除了上述四種較常用的例子外,仍有其他單一結構被發展出來,如斜 邊 (bevel) 結 構 、 溝 槽 式 終 端 結 構 (Trench Termination Technique) <sup>[26-28]</sup>及其他特別的結構等 <sup>[29-30]</sup>等,也都被研究如何有效地整合在功率元件上,主要訴求是將邊界的接面空乏區儘可能的向外延伸,以提高元件邊緣的崩潰電壓。

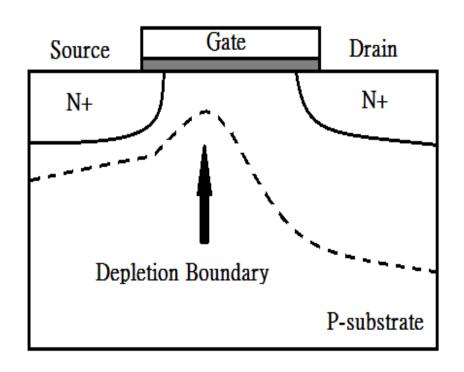

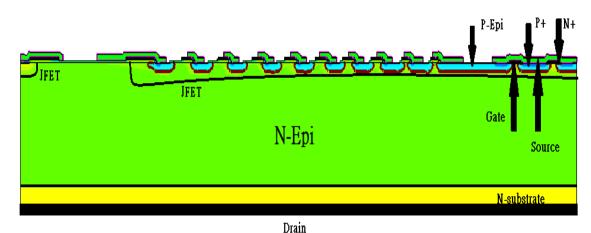

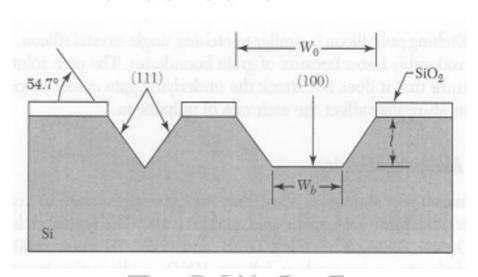

#### **2.4. VDMOSFET (Vertical Double diffused MOSFET)**

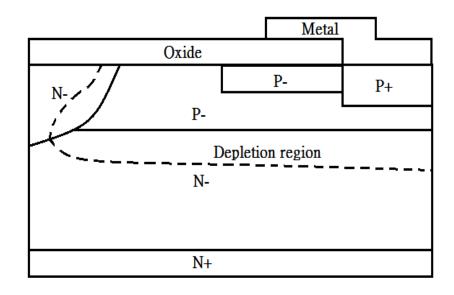

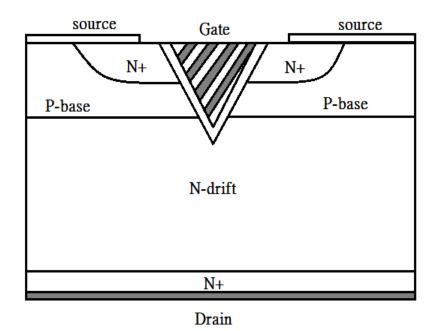

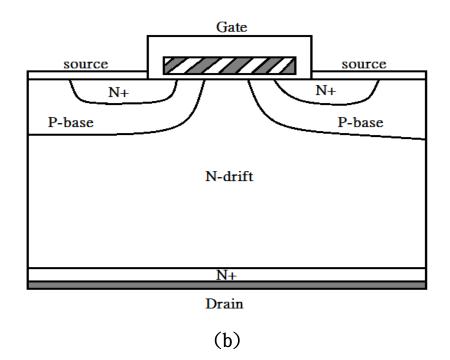

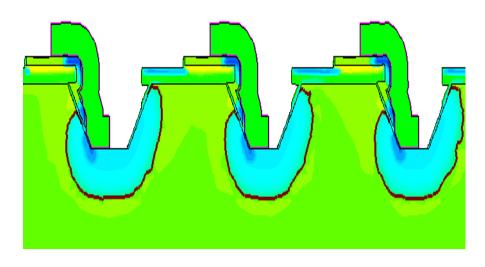

早期的功率金氧半場效電晶體為了耐壓,多半有相當厚度的漂移 區,並以垂直式結構為主,主要分為三類: VMOSFET、DMOSFET、 UMOSFET, 元件結構如圖 2-10 所示。VMOSFET(V-shaped groove MOSFET)又可稱為垂直式V型閘極金氧半場效電晶體,如圖 2-10(a), 是最早發展的垂直式通道功率元件。經由非等向性蝕刻(Anisotropic etching)步驟,形成一個 V 型溝槽的閘極得名,元件的通道則是在 V 型溝槽的邊界形成。VMOSFET 是第一個商業化的 Power MOSFET 產 品,但是它在製程上的不穩定,以及溝槽尖端之過高的電場,使崩潰 易提早發生在 V 形溝槽的尖端,造成耐壓大幅降低。後來被特性較優 的 DMOSFET(Double diffused MOSFET,亦可稱為 VDMOSFET)取代, 如圖 2-10(b)所示。DMOSFET 的 P-base 以及N+源極的區域是同時透 過以閘極光罩的同一擴散窗(Diffusion window)進行自我對齊(Selfalign)的摻雜步驟形成,此元件的閘極平行於晶片表面,稱為平面閘極 (Planar Gate)。最後為垂直式 U 型閘極金氧半場效電晶體(U-shaped groove MOSFET),如圖 2-10(c)

所示。UMOSFET 的結構隨著溝槽蝕刻技術成熟而發展出來,U型閘極結構又稱為溝槽閘極(Trench gate),其操作原理與一般常見的MOSFET 相同,電流的路徑即由表面的源極經過 P-base 區域中的反轉層在至漂移區後到達汲極。UMOSFET 具備較高的導通密度,可有效降低通道電阻,更避免了寄生接面場效電晶體電阻導致的 $R_j$ ,因此整體導通電阻較佳。基本上 UMOSFET 使用反應離子蝕刻(Reactive Ion Etch,簡稱 RIE)型成 U型溝槽,若 U 型溝槽深入漂移區太多,亦會造成崩潰提早發生。

(a)

圖 2-10:(a)垂直式通道金氧半場效電晶體(VMOSFET)結構示意;

- (b)雙擴散式金氧半場效電晶體(DMOSFET)結構示意圖;

- (c)溝槽式金氧半場效電晶體(UMOSFET)結構示意圖

### 第三章: 平面終端結構製程設計與電性 模擬

#### 3.1 平面終端結構

#### 3.1.1 設計原理

本章節將針對金氧半場效電晶體之新型終端結構進行各種參數 模擬,目的是為了提高崩潰電壓和降低終端結構的面積。並且設計元 件在達到崩潰電壓時,崩潰點能遠離核心區域。發生崩潰的地方若能 遠離核心區域,相對散熱性會提高,藉此提高元件承受雪崩崩潰的能 力。最後,對平面結構與V型結構之模擬進行特性比較。

#### 3.1.2 元件結構

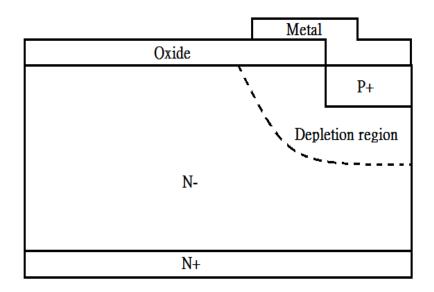

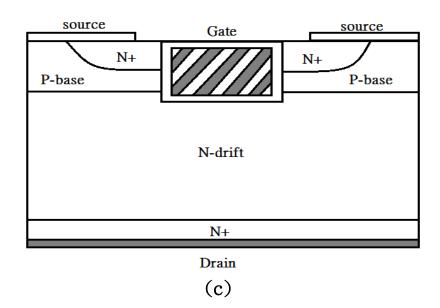

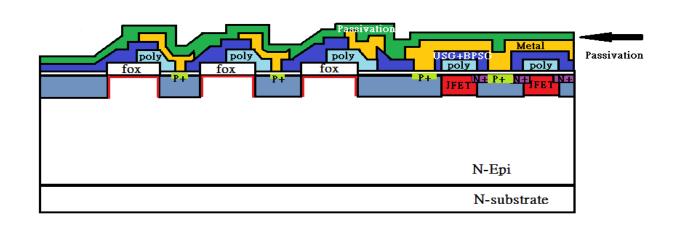

此論文模擬的 VDMOSFET 使用的終端結構為傳統的浮動環搭配場板的結構,圖 3-1 為 VDMOSFET 傳統終端結構示意圖。此結構的浮動環是利用 Field Oxide 當做光罩,與 P-Well 一起佈植形成一圈一圈的浮動環,藉此將電場延伸出去,並搭配上方的場板補助將電場延伸出去。

設計此結構困難的地方在於,每一個 Ring 的濃度與 P-Well 的濃度相同,等於是濃度被限定了,因此只能靠離子佈植時的開口大小,以及開口之間的距離來調整。

終端元件崩潰電壓的定義,我們參照業界的 VDMOSFET 加上終

端結構設計設計出之平面終端結構。

Drain

圖 3-1:傳統平面終端結構圖

#### 3.1.3 製程規劃

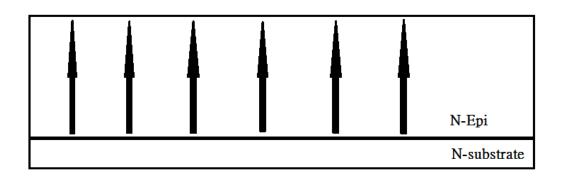

步驟一:準備一個晶格方向為<100>的 №型基板

N-substrate

圖 3-2:製程步驟一

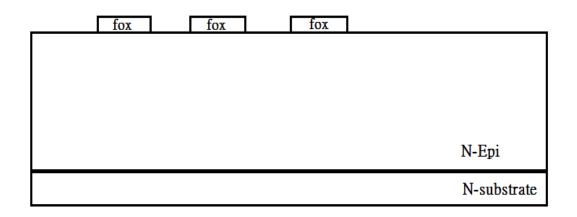

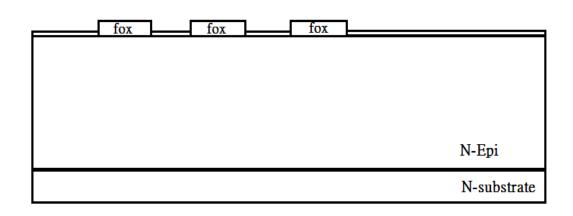

步驟二:在N型基板上使長出厚度約為 50um 的 N-Epi 磊晶層。

圖 3-3:製程步驟二

步驟三:在 N-Epi 上加溫長出一個場區氧化層。

| Field oxide |

|-------------|

|             |

|             |

|             |

| N-Epi       |

| N-substrate |

圖 3-4:製程步驟三

步驟四:利用微影製程使場區氧化層上舖蓋光阻劑。

| photoresist |

|-------------|

| Field oxide |

|             |

|             |

|             |

|             |

|             |

| N-Epi       |

|             |

| N-substrate |

圖 3-5:製程步驟四

步驟五:定義保留與不保留的場區氧化層位置

| photo | photo | photo |              |

|-------|-------|-------|--------------|

|       |       |       | Field oxide  |

|       |       |       |              |

|       |       |       |              |

|       |       |       |              |

|       |       |       |              |

|       |       |       |              |

|       |       |       |              |

|       |       |       | N-Epi        |

|       |       |       | т пр         |

|       |       |       | N-substrate  |

|       |       |       | in-substrate |

圖 3-6:製程步驟五

步驟六:乾蝕刻定義場氧化層然後蝕刻掉全部光阻劑。

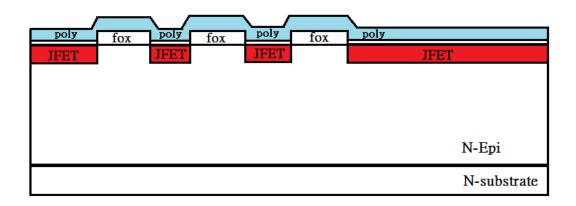

步驟七:再次加溫長襯墊氧化層。

Z 圖 3-8:製程步驟七

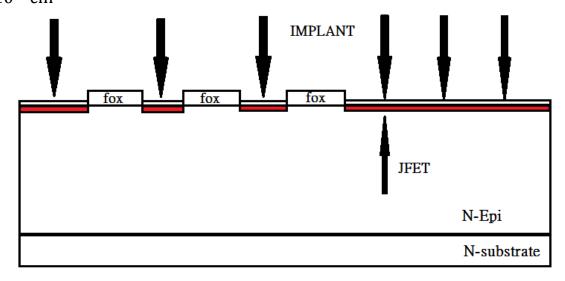

步驟八:利用離子佈植植入磷離子,能量約為 100 keV,劑量為 $6 \times 10^{11} \text{cm}^{-2}$ 。

步驟九:加溫擴散,先移除多餘的氧化層,並再長閘極氧化層。

圖 3-10:製程步驟九

圖 3-11:製程步驟十

步驟十一:利用微影製程定義光阻位置蝕刻複晶矽再佈植硼離子做出 p-well,佈植能量約為 100 keV,劑量為  $2.2 \times 10^{13} \text{cm}^{-2}$ 。

圖 3-12:製程步驟十一

圖 3-13:製程步驟十二

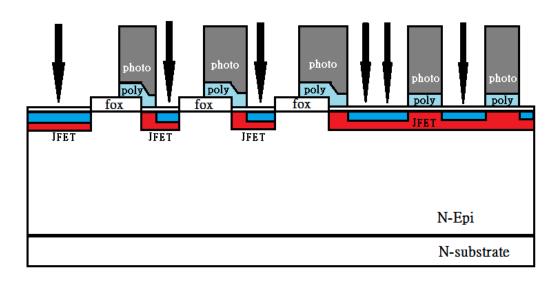

步驟十三:利用微影製程定義 N-well 位置,離子佈植砷離子,能量為 60 keV,劑量為 $8 \times 10^{15} \text{cm}^{-2}$  。

圖 3-14:製程步驟十三

步驟十四:去除光阻,並加溫擴散完成 N-well,蝕刻擴散後所形成的氧化層並在沉積氧化層加溫擴散後,沉積 USG+BPSG,並利用微影製程定義將要做金屬接觸的位置以及P+。

圖 3-15:製程步驟十四

步驟十五:蝕刻 USG+BPSG,移除光阻,離子佈植 BF $_2$ 離子,能量為 100 keV,劑量為 $5 \times 10^{14} \text{cm}^{-2}$ ,離子佈植 B 離子,能量為 120 keV,劑量為 $5 \times 10^{14} \text{cm}^{-2}$ ,去除光阻加溫擴散完成 $P^+$ 。

圖 3-16:製程步驟十五

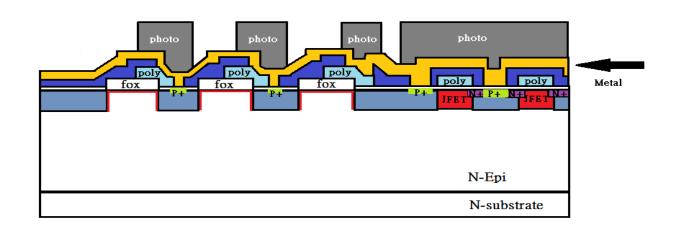

步驟十六:沉積金屬,並使用微影製程定義金屬保留與不保留位置。

圖 3-17:製程步驟十六

步驟十七:蝕刻金屬,移除光阻,最後在表面產生一層緻密的鈍化膜並完成製程。

圖 3-18:製程步驟十七

由上敘製程採用了市面上的參數做參考以及大小,採用 Tsuprem4-Medici 軟體進行製程及元件模擬,設計出 10 個 SiO2 環,如圖 3-19 所示。

圖 3-19:平面終端結構模擬圖

#### 3.1.4 電性模擬

由於這 VDMOSFET 平面終端結構元件是按照市面上的參數設計如圖 3-20 所示,所以分析上固定某些參數,縮小變動範圍,才能觀察自行改變的參數對元件的影響。

Diam

圖 3-20:元件結構參數對應圖

| 濃度參數  | 數值                                                                            |

|-------|-------------------------------------------------------------------------------|

| N-sub | $1 \times 10^{17} \text{cm}^{-3}$                                             |

| N-Epi | 調變(1、3、5、7×10 <sup>14</sup> cm <sup>-3</sup> )                                |

| P-Epi | $2.2 \times 10^{13} \text{cm}^{-2}$                                           |

| N+    | $8 \times 10^{17} \text{cm}^{-2}$                                             |

| P+    | B: $5 \times 10^{14} \text{cm}^{-2}$ BF2: $1.5 \times 10^{14} \text{cm}^{-2}$ |

表 3-1:VDMOS 平面終端結構濃度參數表

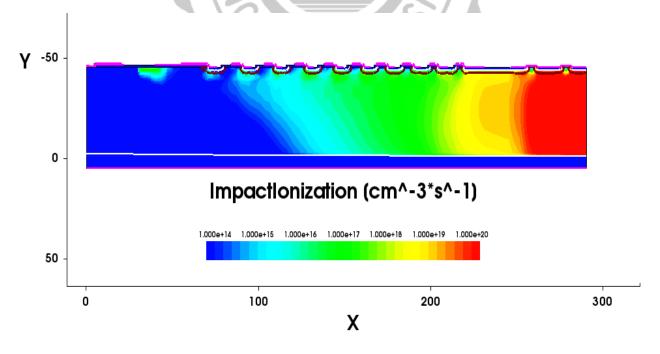

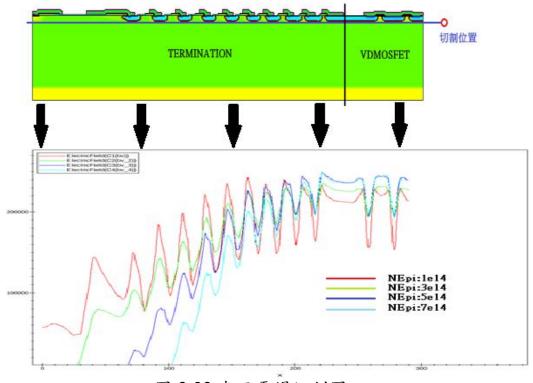

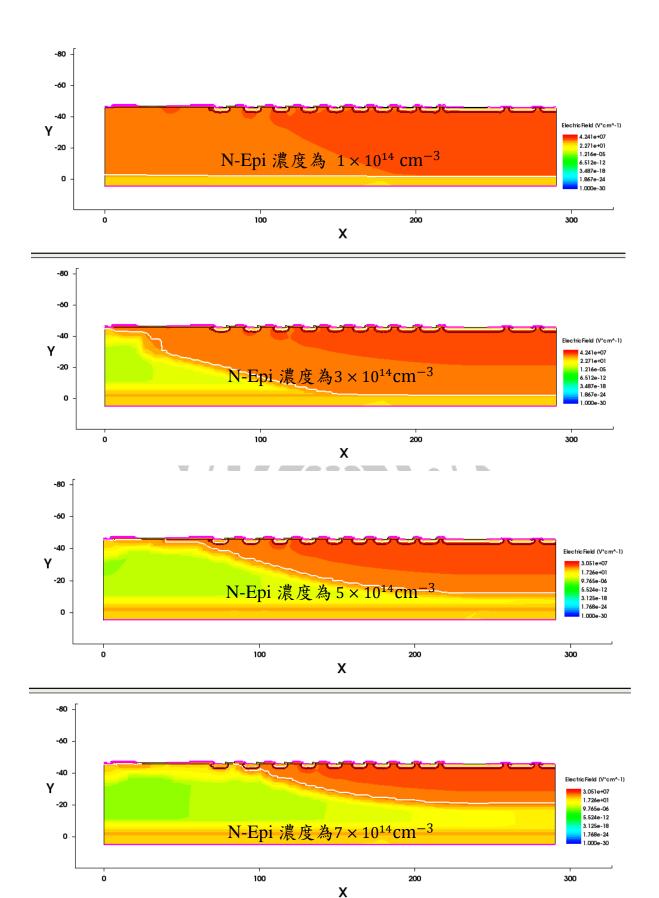

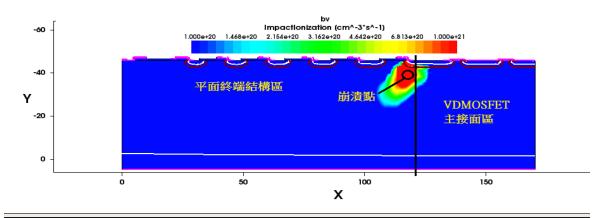

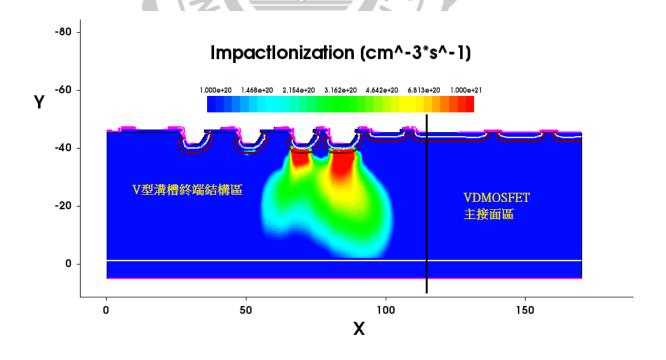

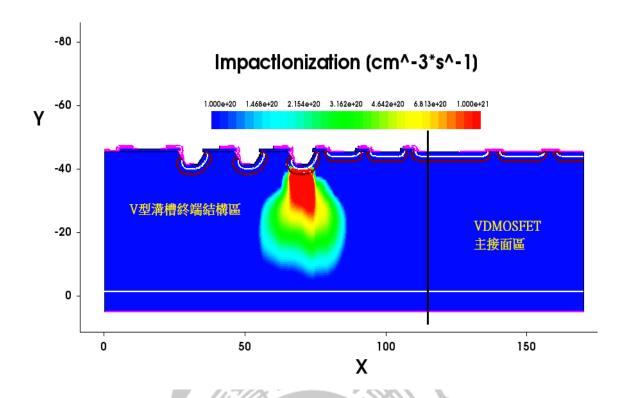

綜合以上表格所列出的參數,即可進行相關參數對電性的模擬與分析,整理出符合設計之規格。在調變 N-Epi 的過程中,使用了以下 幾個濃度去模擬,再根據 IIGR 的分佈做選擇,如下列圖  $3-21(a)1\times10^{14}\,\mathrm{cm}^{-3}$ 、(b) $3\times10^{14}\,\mathrm{cm}^{-3}$ 、(c) $5\times10^{14}\,\mathrm{cm}^{-3}$ 、(d) $7\times10^{14}\,\mathrm{cm}^{-3}$ 。

圖 3-21(a):N-Epi 濃度為 1×10<sup>14</sup> cm<sup>-3</sup>之 IIGR 分佈

圖 3-21(b): N-Epi 濃度為3×10<sup>14</sup>cm<sup>-3</sup>之 IIGR 分佈

圖 3-21(c):N-Epi 濃度為 5×10<sup>14</sup>cm<sup>-3</sup>之 IIGR 分佈

圖 3-21(d): N-Epi 濃度為7×10<sup>14</sup>cm<sup>-3</sup>之 IIGR 分佈

圖 3-22:VDMOSFET 平面終端結構崩潰電壓

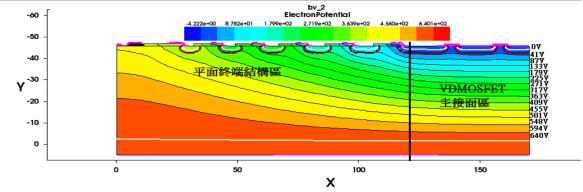

考慮到成本及國內製程水平,故本次研製的 VDMOSFET 採用場限環和場板組合的終端結構。我們可以看到圖 3-22 為 N-Epi 不同濃度的時候所得到的崩潰電壓,得知在1×10<sup>14</sup> cm<sup>-3</sup>、3×10<sup>14</sup>cm<sup>-3</sup>、5×10<sup>14</sup>cm<sup>-3</sup>、7×10<sup>14</sup>cm<sup>-3</sup>,崩潰電壓分別為 750V、585V、420V、320V,也看出了濃度使用越淡則可提升崩潰電壓。若以同樣的製程參數 N-Epi 濃度為1×10<sup>14</sup> cm<sup>-3</sup>模擬 P-i-N 二極體的平行電場其崩潰電壓為770V。所以對應到 N-Epi 濃度1×10<sup>14</sup> cm<sup>-3</sup>的 VDMOSFET 含終端結構之崩潰電壓為750V 是正確的。我們可以明顯的看出空乏區在濃度的淡至濃顯現出的完全空乏與部分空乏影響了崩潰電壓。接著我們切割了這條 VDMOSFET 平面終端結構的表面來看它的電場分佈如圖3-23、24。

圖 3-23:表面電場切割圖

圖 3-24:電場分佈圖

場限環的設計主要考慮的是個數與間距(包括第一個環與主接面間距)、環的接面深度、寬度及濃度。在實際設計中,場限環的接面深度、濃度、寬度往往會受製程等其他因素的制約,是比較容易先確定的,因此主要的優化是環的個數和環間距。對於環的個數,通常來說,耐壓會隨著環數的增加而上升。但是,環數增多也會增大面積。因此設計時要綜合考慮。對於環間距,在確定表面層情況下總是存在一個最佳值,即在一定的環間距時,主接面和各環接面處的電場峰值基本一致,都剛好到達臨界崩潰電場強度,此時可得到最佳的耐壓。

場板設計主要考慮場板長度以及場板與場限環的相對位置。場板越長,空乏區擴展的越寬,崩潰電壓就越高,但是隨著場板長度增加,崩潰電壓不會按比例線性增加,過長的場板反而會降低崩潰電壓,同時也增大了面積。最終,在晶胞核心區方面,綜合考慮崩潰電壓和導通電阻,以及各種濃度的測試,選定磊晶層厚度為 46um,磊晶層濃度為 1x10<sup>14</sup>cm<sup>-3</sup>。根據理論計算,此時主接面的崩潰電壓為 600V,因此根據崩潰電壓 750V 的要求,設計了 9 個 P 環,表面環的寬度依次為 13、11、10、10、10、10、11、12、13 um(自左至右),環與環的間距分別是 8.6、7.5、7.5、6.6、5.5、3.6、3.7、1.7(自左至右)。場板結合採用多晶場板和鋁場板。

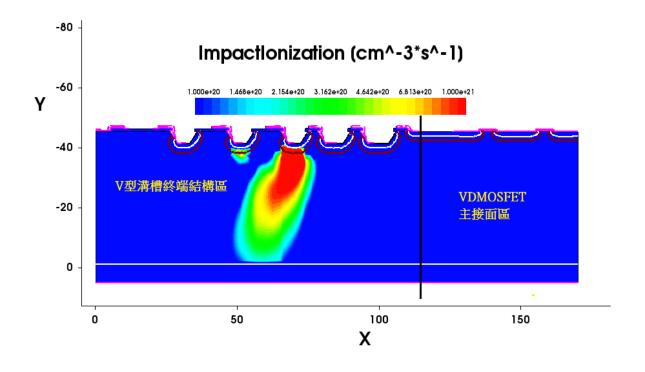

由於圖 3-24 得知, 電場分佈於最右邊的主接面區域也成為了崩

潰電壓所崩潰的區域。為了解決崩潰點在主接面區崩潰的情況,我們採用了V型溝槽終端結構的設計來改善,也在崩潰電壓不變的情況下提升 VDMOSFET 的使用性與耐用性。

# 第四章: V 型溝槽終端結構製程設計與電性模擬

#### 4.1 V 型溝槽終端結構

#### 4.1.1 設計原理

功率 VDMOSFET 元件由於終端接面的曲率效應,其高壓阻斷能力受到限制。為了提高高壓阻斷能力,接面終端技術被廣泛採用,平面終端結構則因為游離碰撞會降低元件的耐用性,深溝槽(deep trench)終端結構使用了昂貴的蝕刻技術,各有其優劣點。本文嘗試以 V 型結構製作終端接面,希望能提高元件的耐用性,同時也解決成本費用過高的問題。溝槽場限環使用了昂貴乾式蝕刻的製程技術感應耦合電漿離子蝕刻技術(Inductively coupled plasma (ICP) reactive ion etcher, RIE),為了減輕製程上的成本,我們改用了氫氧化鉀濕式蝕刻技術(KOH etching),來完成 V 型溝槽的製程。表 4-1 則是氫氧化鉀濕式蝕刻技術的優缺點。

| 濕式蝕刻的優點       | 濕式蝕刻的缺點         |

|---------------|-----------------|

| 高選擇性、儀器成本低、產量 | 等向性的蝕刻輪廓、處理小於   |

| 高、能產生V型蝕刻。    | 3um 圖案的能力差、高度化學 |

|               | 物之使用。           |

表 4-1:KOH 蝕刻優缺點

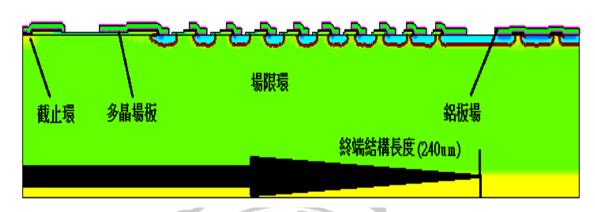

使用氫氧化鉀濕式蝕刻技術在矽晶板上面對於不同的晶格結構 蝕刻的方向也會不同,圖 4-1 為使用氫氧化鉀濕式蝕刻技術在不同晶 格結構的蝕刻趨向。圖 4-2 則為實際使用 Tsuprem4-Medici 軟體進行 製程及元件模擬圖。

## Etching Rate for KOH etching of Si: (100):(110):(111)=100:16:1

圖 4-1:KOH 蝕刻比例圖

圖 4-2:V 型溝槽終端結構模擬圖

#### 4.1.2 改進功率元件模擬

#### 縮減截止區與終端對接面的距離

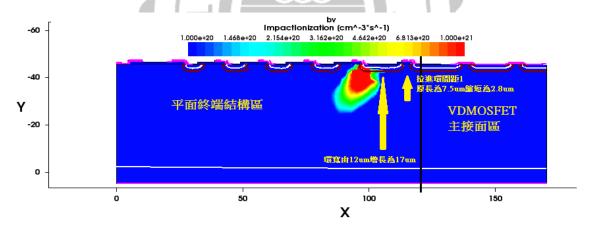

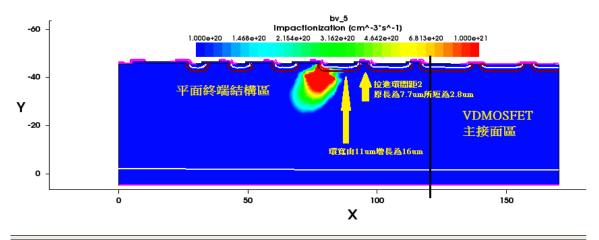

依照第三章的結構,使用 Tsuprem4-Medici 軟體進行製程及元件模擬圖我們先從平面終端結構在每個環上面蝕刻 V 型的溝槽而它的整體長度為 240um,共九個 V 型溝槽深度為 4um,明顯從圖 4-3 看出平面與 V 型終端結構的差別,我們也測試了使用了 V 型終端結構是否影響了崩潰電壓。後續也測試了 V 型溝槽的數量是否也影響了崩潰點以及崩潰電壓。

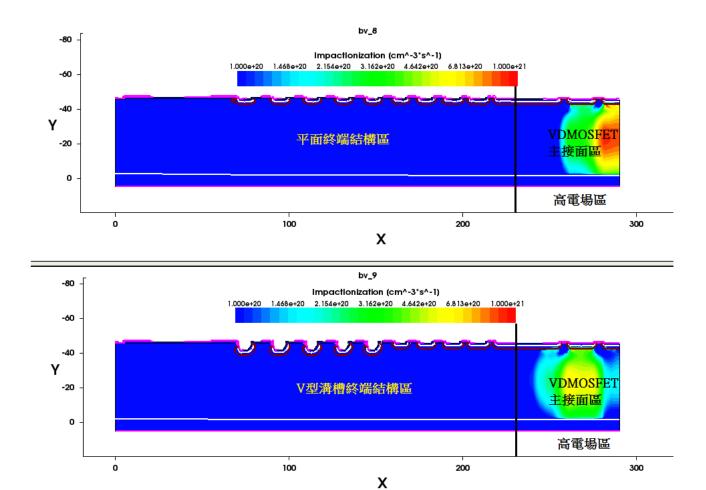

圖 4-3:平面與 V 型溝槽終端結構崩潰電場圖

圖 4-4:平面與 V 型溝槽終端結構崩潰電壓曲線圖

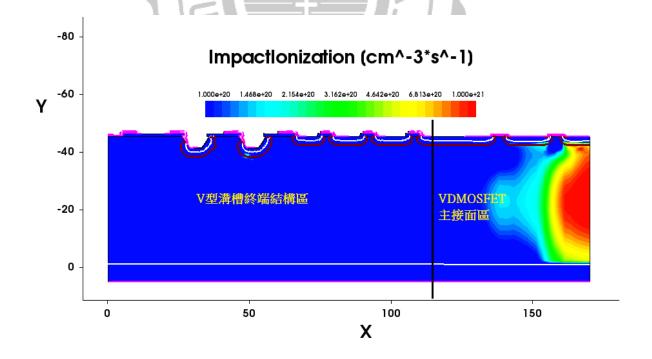

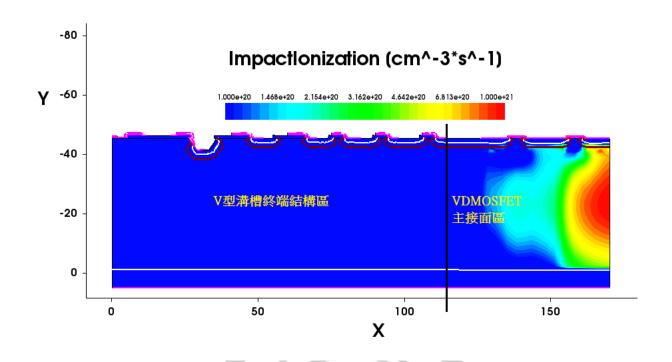

我們從圖 4-3、4-4 來看平面與 V 型溝槽終端結構的崩潰點以及崩潰電壓來看,看出 V 型溝槽比平面的崩潰電壓來的低,而且有 2 個崩潰點分別在終端結構的兩側。通常崩潰點發生在電場最高的地方而集中的地方通常會在尖尖角角的地區,所以在 V 型溝槽結構上可看出崩潰點落在 V 型溝槽的區域,而在平面溝槽我們可崩潰點則在主接面區。雖然 V 型溝槽使得崩潰點遠離了主接面區但是未必能改善崩潰電壓,所以我們測試了許多其他的 V 型溝槽結構。

圖 4-6:6 個與 5 個 V 型溝槽終端結構

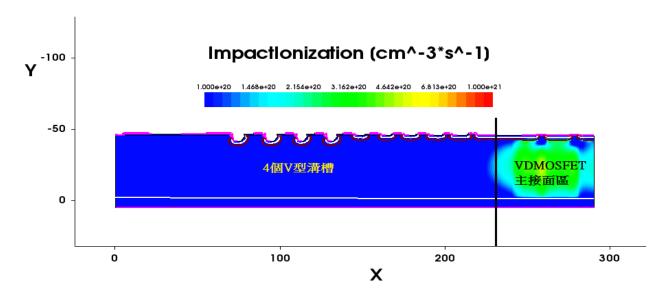

圖 4-7:4 個 V 型溝槽終端結構

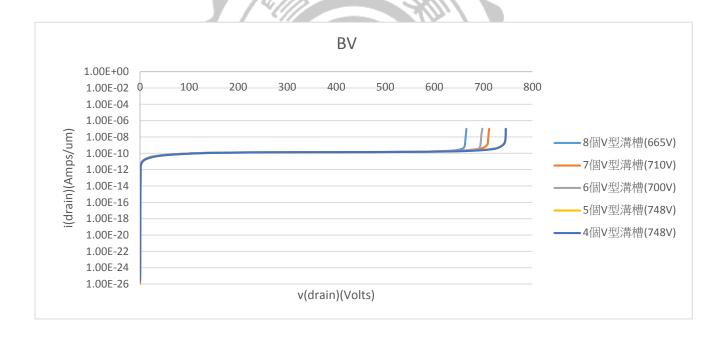

我們測試了從9個V型溝槽減少數量有8、7、6、5與4個。

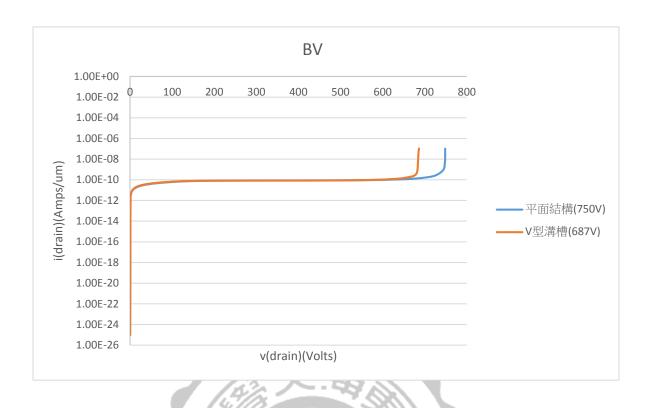

圖 4-8:各溝槽的崩潰電壓曲線圖

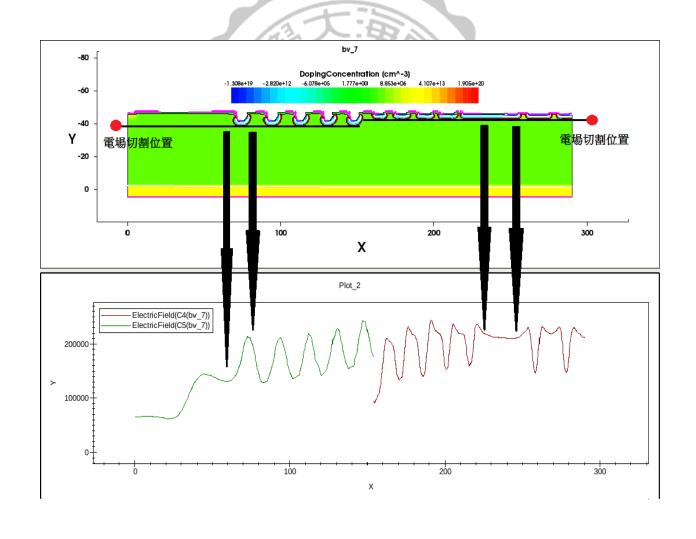

我們從 V 型溝槽的數量不同如圖 4-5、4-6、4-7 所示可以看出崩潰電壓的差別如圖 4-8 所示,使用 V 型溝槽結構依照數量的不同我們可以看出崩潰點會因為終端區的 V 型結構位置而改變崩潰點的地方。

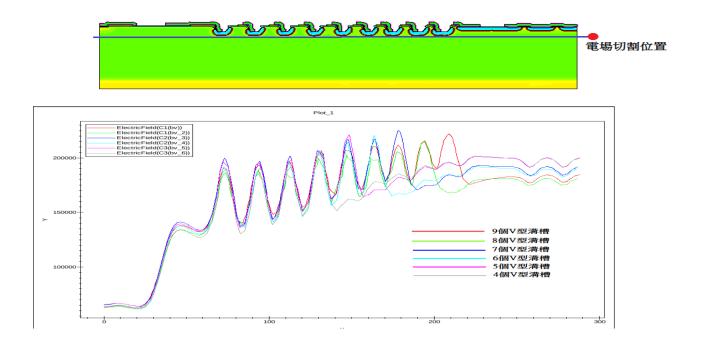

這證明了我們可以使用 V 型的結構來改善崩潰點遠離主核心區域,使得 VDMOSFET 可以提高它的耐用性以及實用性。但是我們發現當 V 型結構數量越來越少從 9、8、7、6 個 V 型溝槽改善崩潰點但是卻無法維持平面結構原來的崩潰電壓 750V,原因是因為高電場分佈縮小導致崩潰電壓降低。所以當設計 V 型溝槽到 5 與 4 個的時候我們看出崩潰點回到原來的主接面區域,崩潰電壓升回了 750V。在此是因為 V 型結構遠離了主接面區域的高電場,無法把高電場分佈到終端結構,這樣又降低了 VDMOSFET 的耐用性以及實用性。我們從圖 4-9 電場的分佈位置可以看出 V 型溝槽的地方能提高電場,使崩潰點遠離主接面區域。

圖 4-9:各 V 型溝槽電場分佈圖

我們最後選擇使用 5 個 V 型溝槽來做分析,因為 5 跟 4 再下去的話崩潰點永遠會在主接面區無法因 V 型結構而調整崩潰點。接著我們切割 V 型溝槽與主接面表面的電場來看,如圖 4-10 所示。加電壓的地方在 VDMOSFET,所以看出兩邊的電場雖然一樣高,但是崩潰卻在主接面區。所以說高電場還沒被 V 型結構給分出去,就已經在主接面區先行崩潰,由這個觀點接下來我們就要解決如何使崩潰點遠離主接面區。

圖 4-10:5 個 V 型溝槽電場切割圖

圖 4-11: 終端結構 240 um 長的電場分布圖 上圖為平面結構下圖為 V 型溝槽結構

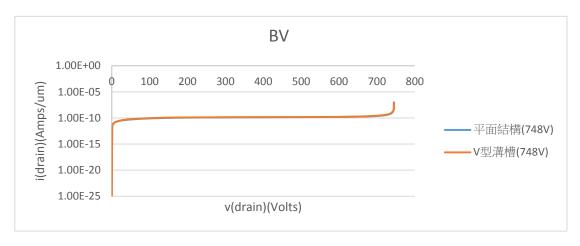

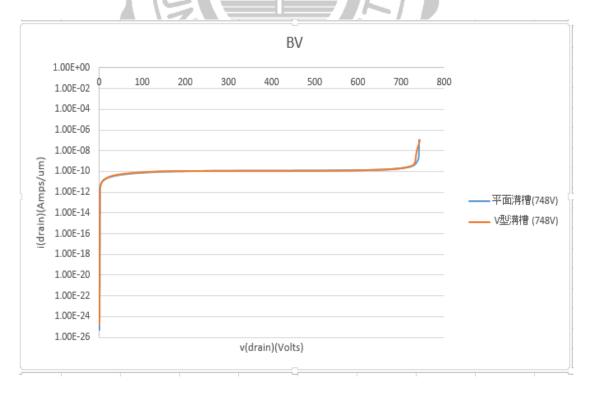

圖 4-11 所示最終從平面與 V 型溝槽得到的電場分布,可以看到, 平面與 V 型溝槽的核心主接面區電場的峰值都極高,也都達到臨界 崩潰電場強度,這說明了會導致元件的耐用性不高。圖 4-12 我們可 以看出崩潰電壓的曲線都是相等的 748V

圖 4-12: 終端結構 240 um 元件的崩潰電壓曲線

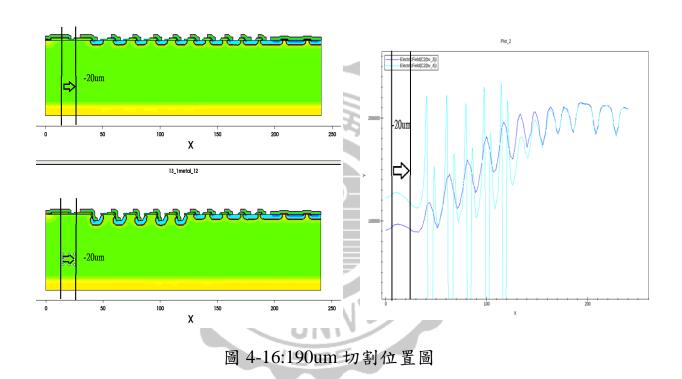

本研究的主題之一是縮小終端結構的面積,因此我們不更改元件的製程條件,而更改光罩上幾何尺寸的設計。圖 4-13 所示,圖的左邊我們選定切割的區域有兩端我們縮小了截止區域的 25um,也縮小了 VDMOSFET 靠近終端結構的距離,用平面的來做比較是要來看相同的情況下影響崩潰點的情形。圖的右邊則為 2 個終端結構的電場。 圖 4-14 是縮短了截止區與主接面間的距離至 190um後的電場分布圖。紅線為平面結構的電場,綠線為 V 型結構的電場。

圖 4-13:240um 切割位置圖

圖 4-14: 終端結構 190 um 長的電場分布圖

上圖為平面結構下圖為V型溝槽結構

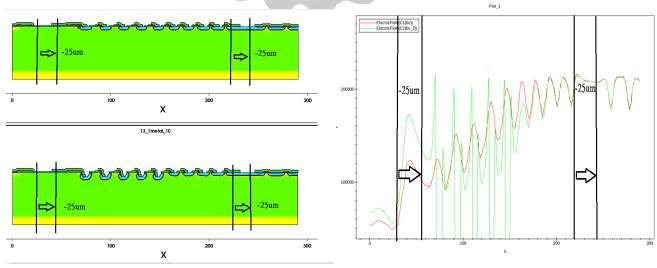

則圖 4-15 為這 2 終端結構的崩潰電壓,維持在 748V。

圖 4-15: 終端結構 190 um 長的崩潰電壓

很不錯的是我們成功縮減了它的面積,但是我們還是發現未必能把崩潰區域移到終端結構上,整體來說可見 VDMOSFET 的高電場還是沒受到 V 型溝槽終端結構的影響,但是可以發現明顯的有把高電場往終端區域延伸,但電場分佈的還是不夠均勻,所以我考慮再縮小面積如圖 4-16。深藍色為平面的電場,淺藍色為 V 型的電場。

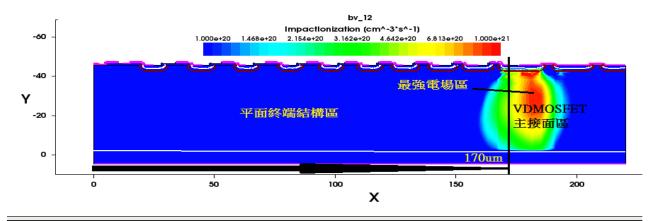

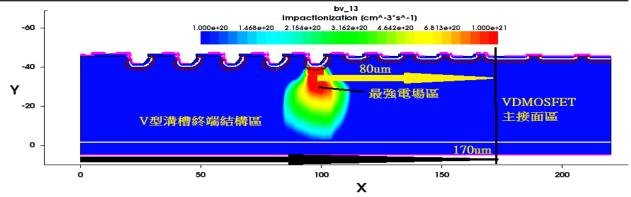

如圖 4-17 我們明顯看出在終端結構長度為 170um 元件的電場分布內,若元件採用平面終端結構則最強電場還是位在於主接面核心區域。若元件採用 V 型溝槽的終端結構則最強電場與主接面核心區域間的距離約為 80um。這證明了 V 型溝槽結構能提升元件的耐用性。圖 4-18 則為崩潰電壓曲線圖。一樣的是 748V。

圖 4-17: 終端結構 170 um 長的電場分布圖

上圖為平面結構下圖為V型溝槽結構

圖 4-18: 終端結構 170 um 長的崩潰電壓

從結構 240um、190um、170um 的終端結構很明顯我們看出電場分布的位置不同,也發現崩潰電壓沒什麼改變的現象。前者原因是因改變電場分布是游離化碰撞通常集中在電場高結構密集的地方,所以從 V 型結構看出,電場集中最高的地方通常是在溝槽的角落,導致雪崩崩潰發生。後者崩潰電壓不變是因為崩潰是接面達到臨界電場時,少數載子會因為強力電場作用而擁有較高的動能,進而產生崩潰效應。這都是電場達到一個定值就會發生的現象,大多是達到2×10<sup>5</sup> (V/cm)時就會發生。電荷密度對空乏區積分就得到電場強度,然而電場強度再對空乏區長度積分一次,就得出電壓值。只要把電場強度用定值的臨界電場代入,就可算出崩潰電壓。而空乏區內部的電荷密度是取決自掺雜濃度,而這3種結構的掺雜濃度是相等的,這也說明了為何電場分布不同卻有相當的崩潰電壓。

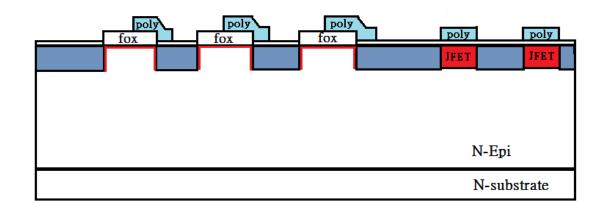

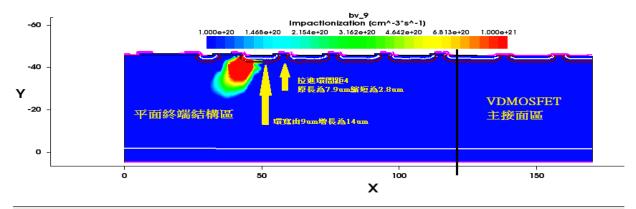

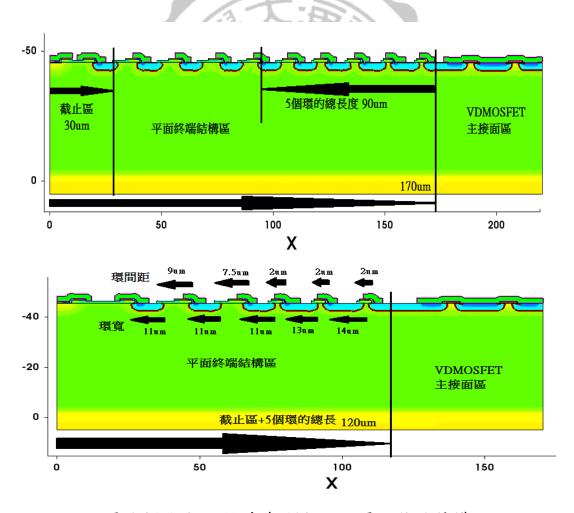

#### 減少V型溝槽終端結構的長度與數量

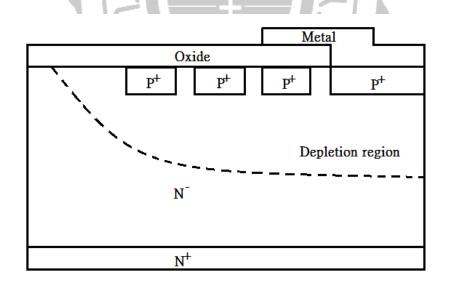

依照市面上有做出終端結構長度為 120um 的平面終端結構而耐壓可達到 700V 以上,本研究試著按照這體積去設計相同長度的平面結構與 V 型溝槽結構的終端結構。因為環的間距以及環寬太小或者太大都會影響製程,所以須要減少 V 型溝槽的數量才能縮小整個 VDMOSFET 終端結構的體積。以下我們嘗試了這些模擬。首先我們須要把平面終端結構的面積也縮小到 120um 才能對此使用 V 型溝槽結構來做比較,在此先來說明一下多場限環結構。才能說明為何縮小面積卻還能提升到 700V 以上。

#### 多場限環結構電壓分佈和邊界峰值電場計算

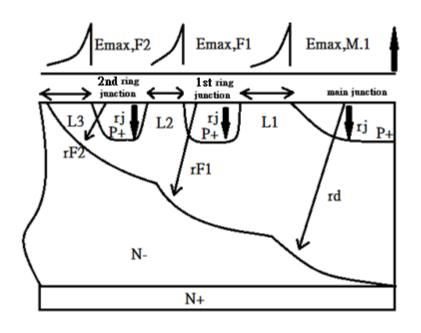

我們這裡將單場限環擴展到多場限環結構,結構圖及空乏區邊界示意圖如圖 4-19 所示,假設存在第 2 個環,且環 1 間距為 L2。由於第一個環受到第二個環的屏遮影響,其使存在第二個環,主接面區的電壓和峰值電場也不會改變,根據這個理論,可以得出,第二個環的存在只影響第一個環的電壓和峰值電場,類似於第一個環對主接面區的影響。

圖 4-19:多場限環結構邊界峰值電場和空乏區外邊界示意圖

多場限環理論<sup>[31-32]</sup> 應滿足:

$$V(n) = V(n-1) + V(n.n-1)$$

(4.1)

式中: V(n)表示第 n 個接面的電位值

V(n-1)表示第 n-1 個接面的電位值

V(n.n-1)表示第n-1個接面和第n個接面距離內環結承擔的電壓。

根據上面的討論,我們可以把第一個接面視為主接面,第二個接面視為第一個場限環來分析各接面的電壓和峰值電場分佈。在沒有第 三個接面存在的情況下,第二個接面電壓和峰值電場如下:

$$V(2) = \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_1)^2}{2} + r_1^2 \ln(\frac{r_1}{r_j + L_2}) - \frac{r_1^2}{2} \right]$$

(4.2)

$$E_{max,F,2} = \frac{qN_d}{2\varepsilon_s} \left[ \frac{r_2^2 - r_j^2}{r_j} \right] \tag{4.3}$$

由於第二個接面的存在,相應第一個接面的電壓和峰值電場也發

生變化,考慮在第二個接面作用後接面1電壓 $V'_{F1}$ ,峰值電場 $E'_{max,F1}$ ,表達式分別如下:

$$V'_{F1} = \frac{qN_d}{2\varepsilon_s} \left(\frac{r_j^2}{2} + r_1^2 \ln\left(\frac{r_j + L_2}{r_j}\right) - \frac{(r_j + L_2)^2}{2}\right)$$

(4.4)

$$E'_{max,F1} = \frac{qN_d}{2\varepsilon_s} \left( \frac{r_1^2 - r_j}{r_j} \right) - \frac{qN_d}{2\varepsilon_s} \left( \frac{r_2^2 - (r_j + L_2)^2}{r_j + L_2} \right)$$

(4.5)

同樣的方法,兩個或者更多的接面的電壓和峰值電場也可以獲得, 通用的表達式如下:

$$V_{i} = \frac{qN_{d}}{2\varepsilon_{s}} \left( \frac{(r_{j} + L_{i})^{2}}{2} + r^{2}_{i-1} ln \left( \frac{r_{i-1}}{r_{j} + L_{i}} \right) - \frac{r_{i-1}^{2}}{2} \right)$$

(4.6)

$$V_{Fi}' = \frac{qN_d}{2\varepsilon_s} \left( \frac{r_j^2}{2} + r_i^2 ln \left( \frac{r_j + L_{i+1}}{r_j} \right) - \frac{(r_j + L_{i+1})^2}{2} \right)$$

(4.7)

$$E_{max,Fi} = \frac{qN_d}{2\varepsilon_s} \left(\frac{r_i^2 - r_j^2}{r_i}\right) \tag{4.8}$$

$$E'_{max,Fi} = \frac{qN_d}{2\varepsilon_s} \left( \frac{r_i^2 - r_j^2}{r_j} \right) - \frac{qN_d}{2\varepsilon_s} \left( \frac{r_j^2 - (r_j + L_{i+1})^2}{r_j + L_{i+1}} \right)$$

(4.9)

其中 i=1,2,3,...,N-1,N 是場限環的個數。最後一個接面, N=i+1,場限環電壓和峰值電場分別為 $V'_{F1}$ , $E'_{max,F1}$ 。

#### 多場限環環間距的優化

根據多場限環結構的理論分析,得到優化環間距和崩潰電壓的步驟如下

- 1. 首先計算出給定接面深度的臨界電場強度  $E_{cc}$

- 2. 由式(4.8)計算在崩潰情況下最外面的空乏區邊界 $r_{max,F,i+1}$

- 3. 將計算出來的  $r_{max,F,i+1}$  代入式(4.6),計算出最外面場限環的崩

潰電壓BV<sub>F,i+1</sub>

- 4. 利用臨界電場計算方程式(4.6),(4.8),然後計算優化的環間距  $L_{opt,i+1}$

- 5.  $r_{max,F,i+1}$  代入(4.7),計算第 i 個場限環接面在崩潰條件下的接面電壓 $BV_{F,I}$ ,可獲得第 i-1 場限環接面的優化環間距  $L_{opt,i+1}$ , $r_{max,F,i-2}$ 。

表達式如下:

$$BV_{i} + BV_{F,i+1} + \dots = \frac{qN_{d}}{2\varepsilon_{s}} \left\{ \frac{(r_{j} + L_{opt,i-1})^{2}}{2} + r_{max,F,i-1} \cdot ln \frac{r_{max,F,i-1}}{r_{j} + L_{opt,i-1}} - \frac{\varepsilon_{s}E_{c}r_{j}}{qN_{d}} - \frac{r_{j}^{2}}{2} - \frac{r_{max,F,i}^{2} - (r_{j} + L_{opt,i-1})^{2}}{r_{j} + L_{opt,i-1}} \cdot \frac{r_{j}}{2} \right\}$$

(4.10)

$$r_{max,F,i-2} = \left\{ \frac{2\varepsilon_s E_c r_j}{qN_d} + r_j^2 + \left[ \frac{r^2_{max,F,i} - (r_j + L_{opt,i-1})^2}{r_j + L_{opt,i-1}} \right] \cdot r_j \right\}^{1/2}$$

(4.11)

其中,i=1,2,3...N-1,N 是環的個數。對於最後一個場限環接面, N=N+1。通過解以上的方程式可以得到主接面和環接面的最佳環間距。 通常,我們根據K. Petrosky D. lampe J. Ostop<sup>[33]</sup>的理論對元件進行一維接面和電場的分析,表明增加場限環後崩潰電壓的增加只與環間距和基板摻雜濃度有關。而實際上,通過上面的理論分析發現相鄰環間電壓是可變的。引起偏差的原因可能是:分析中忽略了主接面區承受的電壓變化,在反偏電壓和環接面電壓的共同作用下這電場會減少,相應的空乏區寬度也會縮小,相鄰環間增加的電壓減少,而不是常數。 因此,在設計場限環時,環間距應該逐漸增大。

## 4.1.3 120um 終端結構改善與模擬

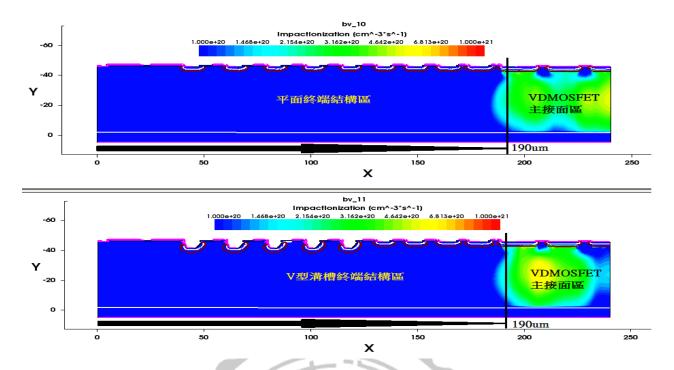

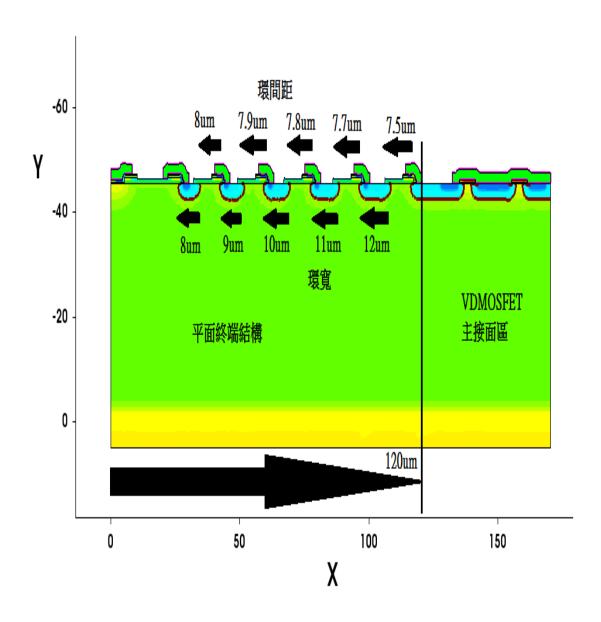

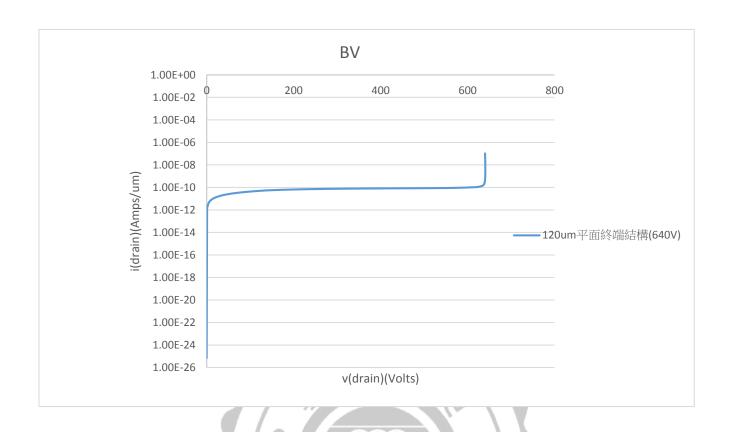

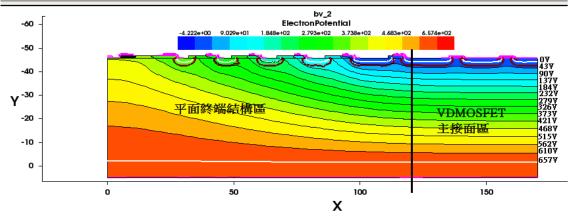

我們依照原先長度 170um 的平面終端結構來縮短他的長度至 120um 如圖 4-20,達到了我們設計要求的目標。但本設計為 120um 比原本的體積還要小,發現設計結構上影響了它的崩潰電壓如圖 4-21。

圖 4-20:120um 平面終端結構

圖 4-21:120um 崩潰電壓曲線圖

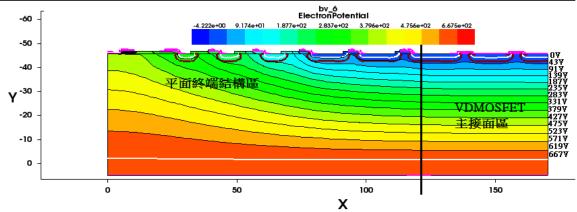

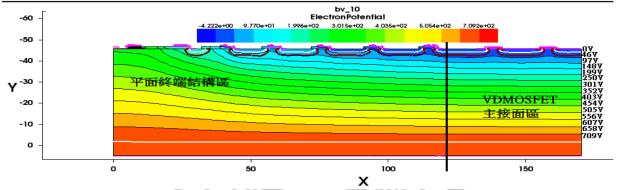

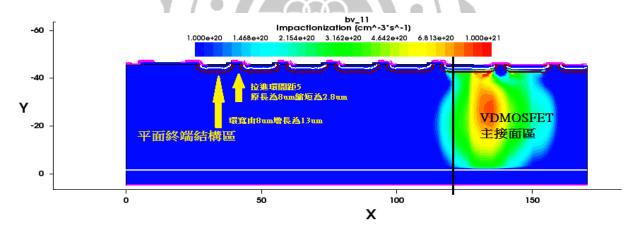

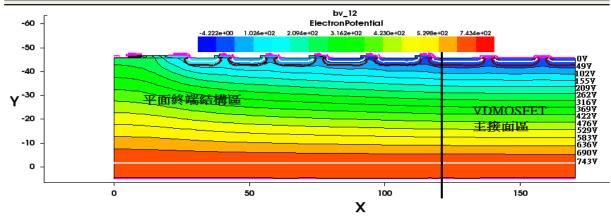

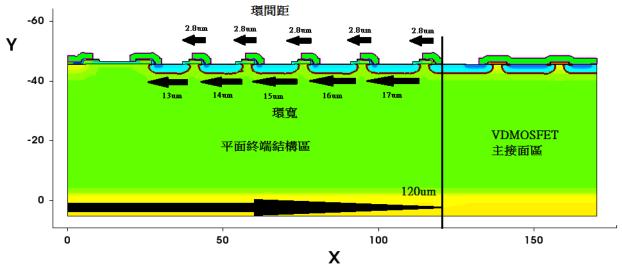

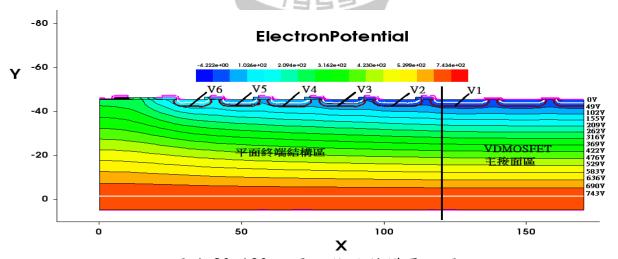

我們查看了崩潰點發現崩潰在靠近主接面區導致電場分布不均 勻,並無把崩潰點往終端結構延伸如圖 4-22。我們了解到崩潰會在環 的周圍,環與環間的距離要靠近才會把崩潰點帶出並延伸出去,已下 我們測試了這幾個方法。我們縮短了環與環之間的距離發現明顯的把 崩潰點延伸至終端區域,如圖 4-23、4-24、4-25、4-26、4-27。並看出 各圖的崩潰電壓如圖 4-28。

4-22:120um 終端結構崩潰區及電位圖

圖 4-23:5 環拉進環間距及電位圖 1(120um)

圖 4-24:5 環拉進環間距及電位圖 2(120um)

圖 4-25:5 環拉進環間距及電位圖 3(120um)

圖 4-26:5 環拉進環間距及電位圖 4(120um)

圖 4-27:5 環拉進環間距及電位圖 5(120um)

圖 4-28:各 5 環拉進環間距之崩潰電壓曲線

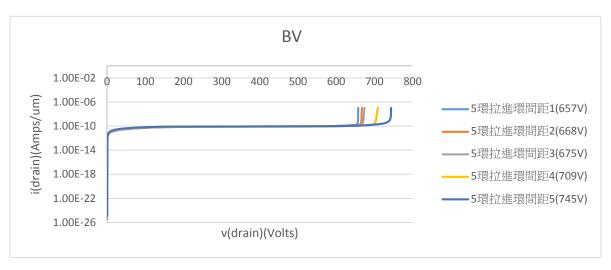

當每個間距都被拉進的時候我們發現依照拉進環間距 1、2、3、4 與 5 崩潰電壓為 657V、668V、675V、709V、745V,依照拉進的間距 我們做了表格對照如表 4-2。雖然第 5 個間距把崩潰電壓提升至 745V, 是一個很不錯的現象而且體積也在 120um 之內,但是崩潰區域很明 顯的回到了主接面區而且還是很一大塊。

|      | 環寬   | 環間距   | 備註     |

|------|------|-------|------|-------|------|-------|------|-------|------|-------|--------|

|      | 5    | 5     | 4    | 4     | 3    | 3     | 2    | 2     | 1    | 1     |        |

| 原始長度 | 8um  | 8um   | 9um  | 7.9um | 10um | 7.8um | 11um | 7.7um | 12um | 7.5um | 圖 4-22 |

| 拉進1  | 8um  | 8um   | 9um  | 7.9um | 10um | 7.8um | 11um | 7.7um | 17um | 2.8um | 圖 4-23 |

| 拉進2  | 8um  | 8um   | 9um  | 7.9um | 10um | 7.8um | 16um | 2.8um | 17um | 2.8um | 圖 4-24 |

| 拉進3  | 8um  | 8um   | 9um  | 7.9um | 15um | 2.8um | 16um | 2.8um | 17um | 2.8um | 圖 4-25 |

| 拉進4  | 8um  | 8um   | 14um | 2.8um | 15um | 2.8um | 16um | 2.8um | 17um | 2.8um | 圖 4-26 |

| 拉進5  | 13um | 2.8um | 14um | 2.8um | 15um | 2.8um | 16um | 2.8um | 17um | 2.8um | 圖 4-27 |

表 4-2:環寬與環間距之前後長度表

從上述公式我們採用了我們最後結果的平面終端結構來做驗證如圖 4-29。

圖 4-29:120um 平面終端結構圖

使用了模擬軟體顯示出了每個電位的分佈及崩潰電壓如圖 4-21。依照公式(4.1)、(4.2)我們來推算出 V1、V2、V3、V4、V5 和 V6 來看理論是否跟模擬軟體上的電位相符。

圖 4-30:120um 平面終端結構電位圖

$$V(n) = V(n-1) + V(n.n-1)$$

$$V_{i} = \frac{qN_{d}}{2\varepsilon_{s}} \left( \frac{\left(r_{j} + L_{i}\right)^{2}}{2} + r^{2}_{i-1} ln\left(\frac{r_{i-1}}{r_{j} + L_{i}}\right) - \frac{r_{i-1}^{2}}{2} \right)$$

式中:

$N_d$ -摻雜濃度(1x10<sup>14</sup>cm<sup>-3</sup>)

$\varepsilon_s$ - $\varepsilon$ 矽的相對介電常數(11.9) ×  $\varepsilon_0$ 真空介電常數(8.85 x10<sup>14</sup>F/cm)

r-距圓柱接面中心的距離  $r2\sim r6$ (4um)

r<sub>i</sub>-接面深度(3um)

L-環間距L1~L6(2.8um)

V-距圓柱結中心為r處的電壓(V2~V6)

q-基本電荷(1.6x10-19C)

根據上面的討論,我們可以把第一個接面視為主接面,第二個接面視

為第一個場限環來分析各接面的電壓分佈。

$$V(2) = \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_1)^2}{2} + r_1^2 \ln(\frac{r_1}{r_j + L_2}) - \frac{r_1^2}{2} \right] = 49V$$

$$V(3.2) = > \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_2)^2}{2} + r_2^2 \ln(\frac{r_2}{r_j + L_3}) - \frac{r_2^2}{2} \right] = 22V$$

$$V(3) = V(2) + V(3.2) = 49V + 22V = 71V$$

$$V(4.3) = > \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_3)^2}{2} + r_3^2 \ln(\frac{r_3}{r_j + L_4}) - \frac{r_3^2}{2} \right] = 22V$$

$$V(4) = V(3) + V(4.3) = 71V + 22V = 93V$$

$$V(5.4) = > \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_4)^2}{2} + r_4^2 \ln(\frac{r_4}{r_j + L_5}) - \frac{r_4^2}{2} \right] = 22V$$

$$V(5) = V(5) + V(5.4) = 93V + 22V = 115V$$

$$V(6.5) = > \frac{qN_d}{2\varepsilon_s} \left[ \frac{(r_j + L_5)^2}{2} + r_5^2 \ln(\frac{r_5}{r_j + L_6}) - \frac{r_5^2}{2} \right] = 22V$$

$$V(6) = V(6) + V(6.5) = 115V + 22V = 137V$$

表 4-3 為實際模擬測出的接面電壓與公式推算出來的接面電壓比較

| 模擬接面電壓  | 推算接面電壓  |

|---------|---------|

| V2=49V  | V2=49V  |

| V3=68V  | V3=71V  |

| V4=94V  | V4=93V  |

| V5=114V | V5=115V |

| V6=137V | V6=137V |

表 4-3 接面電壓比較表

比較起來數值幾乎相符證明了這公式推算是合理的。

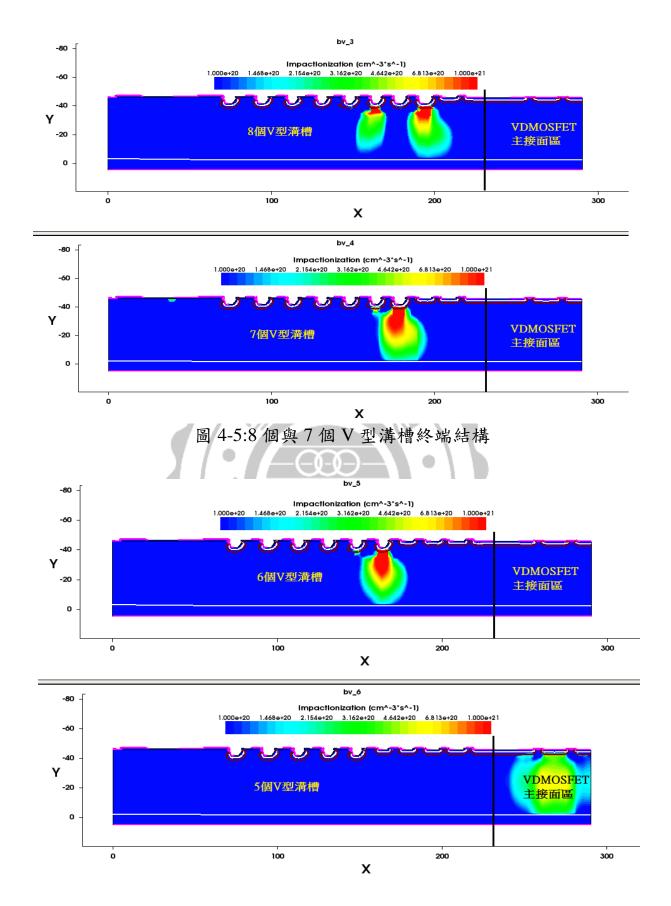

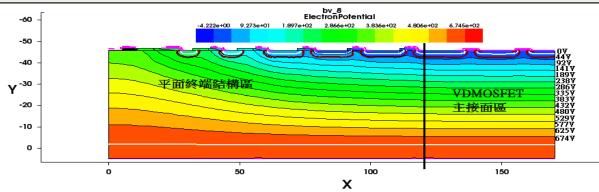

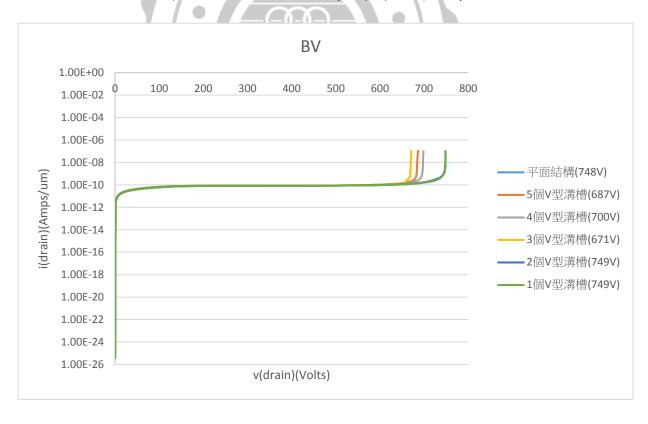

為了把先前 170um 的平面終端結構縮短為 120um 的平面終端結構我們做了結構上的縮減,長度大約是 5 個環的長度 90um 再加上截止環的長度 30um 做一些微調達到長度為 120um 的平面終端結構,如圖 4-31,並使用 V 型溝槽來設計是否也能把崩潰點往終端結構延伸,並也能將崩潰電壓維持在 700V 以上。以下我們做了幾個 V 型溝槽的設計,如圖 4-32、4-33、4-34、4-35、4-36。並從圖 4-37 觀察平面與各溝槽崩潰電壓值。

圖 4-31:170um 縮減為 120um 之平面終端結構

圖 4-32:120um 5 個 V 型溝槽終端結構

圖 4-33:120um 4 個 V 型溝槽終端結構

圖 4-34:120um 3 個 V 型溝槽終端結構

圖 4-35:120um 2 個 V 型溝槽終端結構

圖 4-36:120um 1 個 V 型溝槽終端結構

圖 4-37:120um 平面與各 V 型溝槽崩潰電壓曲線

## 第五章: 結論

本研究的目標是使用 V 型溝槽終端結構提高 VDMOSFET 的耐用性以及實用性,體積縮小至 120um 而崩潰電壓維持在 700V 以上。我們從一開始模擬市面上長度為 290um 的平面終端結構,並將它的長度從 290um 縮短為 240um、190um、170um 及 120um。而長度縮短為 240um、190um、170um 的模擬來看終端結構都是保持在 9 個環,縮短的地方只有主接面區到終端結構的距離以及截止區的距離。考慮到崩潰點的位置都在主接面區以及截止區,所以才會縮短了這 2 個地方,在不影響到崩潰電壓的情況下縮小面積。在縮短的結構內,我們設計了 V 型溝槽,溝槽的數量以及寬深都是探討的範圍,在 9 個環最佳的情況是,減小面積並無影響崩潰電壓的條件下,V 型溝槽終端結構的數量為 5 個平面維持 4 個。

考慮到 120um 的平面終端結構是因為 9 個環長度太長無法再次縮減,必須減少環的數量才能達到縮短到 120um 的效果。所以在 120um 的平面終端結構我們減至 5 個環,也在不影響崩潰電壓的情況下達成了條件。依照九環結構的方式加入了 V 型溝槽的結構,在 120um 的條件下,5 個 V 型溝槽雖然使崩潰點遠離了主接面區,但是 崩潰電壓只有 687V:3 個 V 型溝槽崩潰電壓為 671V,原因是因為雖

然把崩潰點往外延伸了,但是高電場分布太密並無讓電場分佈均勻導致崩潰電壓降低。雖然 2 個和 1 個 V 型溝槽可以使崩潰電壓達到 750V,但是崩潰點卻在主接面區,並無改善 VDMOSFET 的耐用性。 而我們觀察 4 個 V 型溝槽來看,它把崩潰點移至終端結構的中心,有效把崩潰點帶離開了主接面區域,證明了 V 型溝槽在終端結構上在 120um 的長度中,4 個 V 型溝槽與 1 個平面環的終端結構使用是可行的。

本論文對目前已開發的各種 VDMOSFET 終端技術及最新研究和發展進行了研究,並且成功的設計出一款長度為 120um、耐壓 700V的 V型溝槽的 VDMOSFET。在原本的平面結構內加入此 V 型結構可以改變電場分佈,在無損及崩潰電壓的情況下,不但可以縮小元件面積,同時可以使最強電場遠離主接面核心區域,從而增強元件的可靠度。

## 参考文獻

- [1] 劉恩科,朱秉升,羅普生,等.半導體物理學[M]北京:國方工業出版社.1999:1-206

- [2] DE SOUZA M M,SUBHAS C B J V,SANKARA N E M, et al. a novel area efficient floating field limiting ring edge termination technique[J]. Solid-State Electronics, 2000, 44 (8):1381 1386.

- [3] TRAJKOVIC T, UDREA F, WAIND P R, et al. The effect of static and dynamic parasitic charge in the termination area of high voltage device and possible solutions[C]// Proc of ISPSD. Toulouse, France, 2000: 263-266.

- [4] HA M W, LEE S C, CHOI Y H, et al. An improved junction termination design employing shallow trenches and field limiting rings for power devices[J]. JJAP: A, 2006, 44(2): 626-629.

- [5] YO H K, HAN S L, SIN S K, ET AL. A new edge termination technique to improve voltage blocking capability and reliability of field limiting ring for power devices[C]// Proc of ICICDT 2008. Austin, TX, 2008:71-74.

- [6] CHANHO P, JINMYUNG K, TAEHOON K, et al. Deep trench terminations using ICP RIE for ideal breakdown voltages[C]// Proc of ISPSD. 2003: 199-202.

- [7] 施敏.半導體元件物理與技術[M]蘇州:蘇州大學出版社.2004:165-213

- [8] CLARK L. Enchancement of breakdown properties of overlay annual diodes by field shaping resistive films [J]. Solid-State Electronics. 1972,15(6):653-657.

- [9] MATSUSHITA T, AOKI T, YAMAOTO T, et al. Highly reliable high-voltage transistors by use of the SIPOS process [J].IEEE Trans on ED . 1976, 23(8):826-830

- [10] FEILER W, FALCK E, GERLACH W. Multistep field plates for high-voltage planar p-n junctions[J]. IEEE Trans on ED. 1992, 39(6):1514-1520.

- [11] 張彥飛、吳郁、遊雪蘭,等.矽材料功率半導體元件結終端技術的新發展[J].電子元件,2009,32(3):538-546

- [12] 陳星粥.功率 MOSFET 與高壓整合電路[M].南京:東南大學出版 社.1990:122-222

- [13]王英、何杞鑫、方紹華.高壓功 VDMOS 管的設計研制[J].電子原件,2006.29(1):5-8.

- [14] 趙麗霞、袁肇耿、張鶴鳴.高壓 VDMOS 用外延片的外延參數設計 [J] 半導體技術,2009.34(4):348-350

- [15]B.J. Baliga, Fundamentals of power Semiconductor

- [16]Donald A. Neamen, Semiconductor Physics and Devices: Basic Principles(4e)

- [17]G. Charitat, "Voltage handling capability and termination techniques of silicon power semiconductor devices," bipolar/BiCMOS Circuits and Technology Meeting, Proceedings of the 2001, pp. 175-183.

- [18]D.S.Chao, C.C Hung, D.Y.shu, M.-J. Kao, and W.Y. Hsieh; M.-J. Tsai; Benson Wang; Bill Teng; H.P. Tsai; Rick Lin; Max Chen," Optimization and fabrication of planar edge termination techniques for a high breakdown voltage and low leakage current p-i-n diode," Applied Power Electronics Conference and Exposition, 2004. APEC `04. Nineteenth Annual IEEE, Vol.1, pp. 241-245,2004

- [19]Z. Hossain, T. Ishigwo, L. Tu, H. Corleto, F. Kuramae, and R. Nair," Field-plate effects on the breakdown voltage of an integrated high-voltage LDMOS transistor," Power Semiconductor Devices and ICs, 2004. Proceedings. ISPSD `04. The 16<sup>th</sup> International Symposium on 24-27 May 2004,pp.237-240.

- [20] A.Nezar and C.A.T. Salama, "Breakdown voltage in LDMOS transistors using internal field rings," Electron Devices, IEEE Transactions on Vol.38, Issue 7, July 1991,pp.1676-1680.

- [21] M. Vellvehi, D. Flores, and Joreda .X et. Al. "Design and optimization of suitable edge terminations for 6.5kv IGBTs," Microelectronics Journal, Vol. 33, Issue9, September 2002,pp.765-769.

- [22] A.W. Ludikhuize," A Review of RESURF Technology," in Proceedings of 2000 International Symposium on power Semiconductor Device and ICs,pp.11-18, May 2000.

- [23]J.A. Appels and H.M.J Vaes, "High Voltage Thin Layer Devices(RESURF Devices)," Proceeding of 25<sup>th</sup> International electron Device Meeting, IEEE-IEDM 1979, Vol.25, pp.238-241.

- [24]Z.Parpla and C.A.T Salama, "Optimization of RESURF LDMOS transistors: an analytical approach," IEEE Transactions on Electron Devices, Vol.37, Issue 3,pp. 789-796, March 1990.

- [25] A. Aarts and N. D'Halleweyn, "A surface-potential-based high voltage compact LDMOS transistor Model, "Electron Devices, IEEE Transactions on, Vol.52, Issue 5 May 2005,pp. 999-1007.

- [26]D.Dragomirescu, G.. Charitat, and F. Morancho," Novel concepts for high voltage junction termination techniques using very deep trenches," in Proceedings of 1999 Semiconductor Conference, Vol.1, 5-9 Oct.1999 pp. 67-70.

- [27]D.Dragomirescu and G.Charitat," Trench termination technique with vertical JTE for 6kV devices," in Precedings of 2000 Bipolar/BiCMOS Circuits and Technology Meeting, 24-26 Sept. 2000 pp. 86-89

- [28]L.Theolier et al. " A New junction termination technique: the Deep

- Trench Termination(DT2)," Proc. Of ISPSD'2009, pp. 176-179, 2009.

- [29]J.K. Oh, M.W. Ha, M.K. H, and Y.I. Choi, "A new junction termination method employing shallow trenches filled with oxide," Electron Device Letters, IEEE Vol.25, Issue 1, Jan. 2004, pp. 16-18.

- [30]D. Krizaj, S. Amon, and G. Charitat, "Diffused spiral junction termination structure: modeling and realization," in Proceedings of 1996 International Symposium on Power Semiconductor Devices and ICs, 20-23 May 1996, pp. 247-250.

- [31] V.A.K. Temple and M.S. Adler, "Calculation of the Diffusion Curvature Related on Electron Devices, Vol. ED-22,pp. 910-916, 1975.

- [32]B.J. Baliga and S.K. Ghandhi, "Analytical Solutions for the Breakdown Voltage of Abrubt Cylindrical and Spherical Junctions", Solid-State Electronics, Vol. 19,pp. 739-744,1976.

- [33]K.Petrosky D.lampe J.Ostop Westinghouse electric corp Baltimore "Estimate of increase of planar junction breakdown voltage with field limiting ring" [J]\_IEEE md21203, P674-677 1988